Renesas RZ/N2L-RSK

Contents

This article describes specifics for the Renesas RZ/N2L-RSK evaluation board.

Minimum requirements

- J-Link software V7.70a or later

Preparing for J-Link

- Connect the J-Link to the debug header (J13 or J20)

- Power the board via USB C (CN5) or external power supply / power jack (CN6)

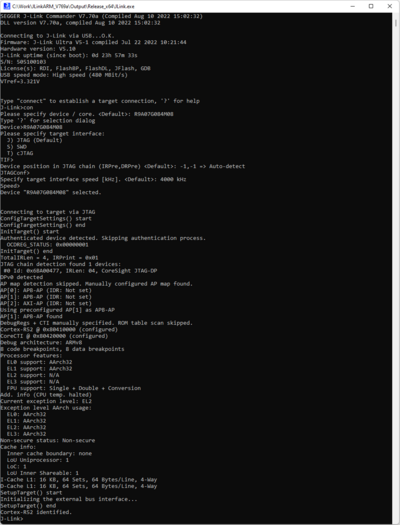

- Verify the Connection with e.g. J-Link Commander. The output should look as follows:

NOR flash programming

Board Preparation

- Check whether SW4 on RZ/N2L RSK board is set as 16bit bus boot mode(NOR flash):

<SW4> (16bit bus boot mode (NOR flash)): 1-ON; 2-OFF; 3-ON; 7-OFF

<CN24> Short 1-2

<CN17> Short 1-2 - Power on reset the RZ/N2L RSK board

Test Procedure

- Start J-Link Commander

JLink.exe -device R9A07G075M0 -if SWD -speed 12000 -autoconnect 1 - Enter the following commands

r

loadfile 1MB_TestData.bin,0x70000000 - Repeat the loadfile sequence several times

Expected result: Programming skipped - Enter the following commands

r

exec setcomparemode 0

loadfile 1MB_TestData.bin,0x70000000 - Repeat the loadfile sequence several times

Expected result: Programming will be executed each time because compare step is skipped

Example Project

TBD

SETUP

TBD