Synergy

Contents

This article describes device specifics of the Renesas Synergy microcontrollers.

Option byte programming

To program the option bytes starting at address 0x01010008 (0x0100A150 for the S5D9), within Synergy device series, it is necessary to program the complete option byte sector starting from address 0x01010008 to address 0x01010033 (0x0100A150 to 0x0100A16F for the S5D9), also bytes that shall not be modified.

In case of programming only parts of the option bytes, the flash algorithm also tries to erase the non-modified bytes within the option byte sector. Due to the fact that certain bits cannot be erased after being programmed once the subsequent verification of the option byte sector fails, when these bits remain '0'. In this case further programming of remaining sections is aborted.

Using SWO on Synergy Devices

In general, the J-Link DLL expects the trace clock to be equal to the CPU clock. As the Synergy device series allows to enable a pre-scaler which is valid for trace clock only, this assumption may be incorrect resulting in invalid SWO data are read. To make sure that the J-Link DLL behaves as expected, please make sure to not enter the actual CPU clock but the CPU clock multiplied with the ICKdivider configured in the System Clock Division Control Register (SCKDIVCR) divided by the trace clock divider configured in the Trace Clock Control Regigster (TRCKCR). Further information regarding this can be found in the two examples below.

Example (S3A7)

- MOCO (8MHz)

- System Clock Division Control Register (SCKDIVCR[ICK[2:0]]): 0x4 --> * 1 / 16

- System Clock Source Control Register (SCKSCR[CKSEL[2:0]]): 0x1 --> MOCO selected as source for the ICLK (System Clock) and TRCLK (Trace Clock)

- Trace Clock Control Register (TRCKCR[TRCK[3:0]]): 0x1 --> /2

- ICLK = 8MHz * 1 / 16 = 500 kHz CPU clock

- TRCLK = ICLK * 1 / 2 = 250 kHz Trace / SWO clock

CPU clock to be entered in the IDE project = ICLK * ICKdivider / TRCKdivider = 500 kHz * 16 / 2 = 4 MHz

Example (S7G2)

- MOCO (8MHz)

- System Clock Division Control Register (SCKDIVCR[ICK[2:0]]): 0x4 --> * 1 / 4

- System Clock Source Control Register (SCKSCR[CKSEL[2:0]]): 0x1 --> MOCO selected as source for the ICLK (System Clock) and TRCLK (Trace Clock)

- Trace Clock Control Register (TRCKCR[TRCK[3:0]]): 0x1 --> /2

- ICLK = 8MHz * 1 / 4 = 2 MHz CPU clock

- TRCLK = ICLK * 1 / 2 = 1 MHz Trace / SWO clock

CPU clock to be entered in the IDE project = ICLK * ICKdivider / TRCKdivider = 2 MHz * 4 / 2 = 4 MHz

Synergy S1 R7FS12477

Tracing on Renesas Synergy S1 R7FS12477

This article describes how to get started with trace on the Renesas Synergy S1 R7FS12477 MCU. This article assumes that there is already a basic knowledge about trace in general (what is trace, what different implementations of trace are there, etc.). If this is not the case, we recommend to read Trace chapter in the J-Link User Manual (UM08001). The Renesas Synergy S1 R7FS12477 MCU implements tracing via via on-chip trace buffer (MTB), so a J-Link can be used for tracing. Tracing over pins is not supported by this target device.

Minimum requirements

In order to use trace on the Renesas Synergy S1 R7FS12477 MCU devices, the following minimum requirements have to be met:

- J-Link software version V6.72b or later

- Ozone V3.20 or later (if trace and / or the sample project from below shall be used)

- J-Link Plus V10 or higher

To rebuild the project our IDE Embedded Studio can be used. The recommended version to rebuild the projects is V6.30. But the examples are all prebuild and work out-of-the box with Ozone, so rebuilding is not necessary.

Sample project

MTB trace

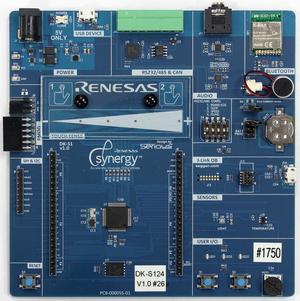

The following sample project is designed to be used with J-Link Plus and Ozone to demonstrate MTB trace. The project has been tested with the minimum requirements mentioned above and a DK-S124 evaluation board. The sample project comes with a pre-configured project file for Ozone that runs out-of-the box. In order to rebuild the sample project, SEGGER Embedded Studio can be used.

The MTB does not support streaming trace.