Arm trace technical specification

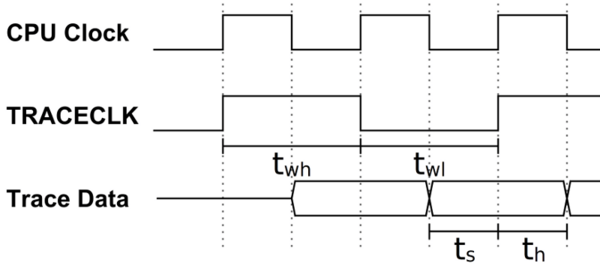

When using the J-Trace PRO as a debugging tool it is crucial for a successful session that the trace data output by the microcontroller is meeting specific timing requirements. The trace clock speed (TRACECLK) is on most microcontrollers directly dependent on the CPU clock speed and is usually half of the CPU clock speed.

Contents

Arm trace timing requirements

Arm defines the trace timing requirements as follows:

| Signal name | Description | Value |

|---|---|---|

| twl | TRACECLK LOW pulse width | Min. 2 ns |

| twh | TRACECLK HIGH pulse width | Min. 2 ns |

| tr/tf | Clock and data rise/fall time | Max. 3 ns |

| ts | Data setup time | Min. 3 ns |

| th | Data hold time | Min. 2 ns |