Difference between revisions of "J-Link-OB-K22-SiFive"

| Line 4: | Line 4: | ||

= Debug interface = |

= Debug interface = |

||

| + | This J-Link OB provides the following debug interfaces to debug the target MCU mounted on the eval board: |

||

| + | * JTAG (4-wire JTAG, IEEE 1149.1) |

||

| + | |||

| + | == JTAG == |

||

| + | The JTAG debug interface specifies uses the following pins on the J-Link OB: |

||

| + | * PTD5 (TCK) |

||

| + | * PTD6 (TMS) |

||

| + | * PTD2 (TDI) |

||

| + | * PTE1 (TDO) |

||

| + | * PTD7 (nRESET) |

||

| + | |||

| + | '''Note:''' The JTAG interface is tri-stated while there is no active debug connection to the J-Link OB. This means while there is no IDE or other application that has an open connection to the J-Link OB, the J-Link OB will tri-state its JTAG pins. This is to make sure that an external JTAG connector may be mounted on the board to also allow to use external J-Links etc. to debug the target MCU on the board |

||

| + | |||

| + | == Reset pin == |

||

| + | The debug interface also specifies a reset pin that is used to reset the target MCU on the board. The reset pin has a defined active LOW logic. J-Link controls this pin as open-drain, meaning that it only actively pulls the pin LOW in case a reset request comes from a host software connecting to the J-Link OB via USB. HIGH levels are generated by the J-Link OB releasing the reset line and let an internal pull-up resistor pull the line HIGH. This logic allows to have a reset button on the board as well, so button pushes do not interfere with the J-Link OB reset line control. |

||

= VCOM support = |

= VCOM support = |

||

| − | The J-Link-OB-K22-SiFive supports 2 VCOM ports that are accessible from the host (PC) side. |

+ | The J-Link-OB-K22-SiFive supports 2 VCOM ports (VCOM0 and VCOM1) that are accessible from the host (PC) side. |

== Pin usage == |

== Pin usage == |

||

| Line 21: | Line 36: | ||

== RTS behavior == |

== RTS behavior == |

||

| − | The RTS line of J-Link is used to reset the ESP32 WiFi device on the eval board the OB is mounted on. It has an active LOW logic. The pin may be controlled from the host side for example via Python calls. The following behavior was explicitly requested by SiFive to make the J-Link OB mimic the behavior of simple USB to serial |

+ | The RTS line of J-Link VCOM0 is used to reset the ESP32 WiFi device on the eval board the OB is mounted on. It has an active LOW logic. The pin may be controlled from the host side for example via Python calls. The following behavior was explicitly requested by SiFive to make the J-Link OB mimic the behavior of simple USB to serial adapters: |

{| class="wikitable" |

{| class="wikitable" |

||

|- |

|- |

||

! Python call !! Physical RTS level |

! Python call !! Physical RTS level |

||

|- |

|- |

||

| + | | Ser.setRTS(True) || J-Link OB pulls line LOW |

||

| − | | xxx || xxx |

||

|- |

|- |

||

| + | | Ser.setRTS(False) || J-Link OB release pin and pull-up resistor pulls line HIGH |

||

| − | | xxx || xxx |

||

|} |

|} |

||

| − | |||

| − | TBD |

||

== DTR behavor == |

== DTR behavor == |

||

| + | The DTR line of J-Link VCOM1 is used as a boot pin for the ESP32 WiFi device on the eval board the OB is mounted on. The pin may be controlled from the host side for example via Python calls. The following behavior was explicitly requested by SiFive to make the J-Link OB mimic the behavior of simple USB to serial adapters: |

||

| − | TBD |

||

| + | {| class="wikitable" |

||

| + | |- |

||

| + | ! Python call !! Physical DTR level |

||

| + | |- |

||

| + | | Ser.setDTR(True) || J-Link OB pulls line LOW |

||

| + | |- |

||

| + | | Ser.setDTR(False) || JLink OB release pin and pull-up resistor pulls line HIGH |

||

| + | |} |

||

| + | |||

= WebUSB support = |

= WebUSB support = |

||

Revision as of 11:51, 11 November 2019

This article describes specifics of the J-Link OB K22 SiFive.

Contents

Debug interface

This J-Link OB provides the following debug interfaces to debug the target MCU mounted on the eval board:

- JTAG (4-wire JTAG, IEEE 1149.1)

JTAG

The JTAG debug interface specifies uses the following pins on the J-Link OB:

- PTD5 (TCK)

- PTD6 (TMS)

- PTD2 (TDI)

- PTE1 (TDO)

- PTD7 (nRESET)

Note: The JTAG interface is tri-stated while there is no active debug connection to the J-Link OB. This means while there is no IDE or other application that has an open connection to the J-Link OB, the J-Link OB will tri-state its JTAG pins. This is to make sure that an external JTAG connector may be mounted on the board to also allow to use external J-Links etc. to debug the target MCU on the board

Reset pin

The debug interface also specifies a reset pin that is used to reset the target MCU on the board. The reset pin has a defined active LOW logic. J-Link controls this pin as open-drain, meaning that it only actively pulls the pin LOW in case a reset request comes from a host software connecting to the J-Link OB via USB. HIGH levels are generated by the J-Link OB releasing the reset line and let an internal pull-up resistor pull the line HIGH. This logic allows to have a reset button on the board as well, so button pushes do not interfere with the J-Link OB reset line control.

VCOM support

The J-Link-OB-K22-SiFive supports 2 VCOM ports (VCOM0 and VCOM1) that are accessible from the host (PC) side.

Pin usage

On the J-Link OB side, the following pins are used for VCOM:

VCOM0

- PTB16 (J-Link Rx)

- PTB17 (J-Link Tx)

VCOM1

- PTC1 (J-Link RTS)

- PTC3 (J-Link Rx)

- PTC4 (J-Link Tx)

- PTC5 (J-Link DTR)

RTS behavior

The RTS line of J-Link VCOM0 is used to reset the ESP32 WiFi device on the eval board the OB is mounted on. It has an active LOW logic. The pin may be controlled from the host side for example via Python calls. The following behavior was explicitly requested by SiFive to make the J-Link OB mimic the behavior of simple USB to serial adapters:

| Python call | Physical RTS level |

|---|---|

| Ser.setRTS(True) | J-Link OB pulls line LOW |

| Ser.setRTS(False) | J-Link OB release pin and pull-up resistor pulls line HIGH |

DTR behavor

The DTR line of J-Link VCOM1 is used as a boot pin for the ESP32 WiFi device on the eval board the OB is mounted on. The pin may be controlled from the host side for example via Python calls. The following behavior was explicitly requested by SiFive to make the J-Link OB mimic the behavior of simple USB to serial adapters:

| Python call | Physical DTR level |

|---|---|

| Ser.setDTR(True) | J-Link OB pulls line LOW |

| Ser.setDTR(False) | JLink OB release pin and pull-up resistor pulls line HIGH |

WebUSB support

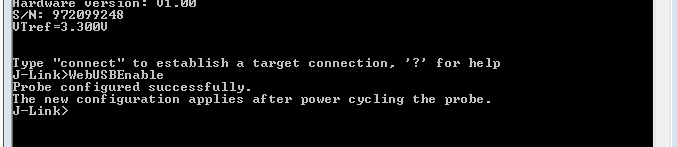

The J-Link OB K22 SiFive supports WebUSB for firmware build compiled Jul 30 2019 12:24:12 (delivered with V6.48a of the J-Link software) and later. By default, WebUSB support is not enabled on the Ob and needs to be enabled per one-time setup. In the following, it is assumed that it is already known what WebUSB is and what it can be used for. For more information, please refer to the WebUSB wiki article.

Enabling WebUSB

In order to enable WebUSB, J-Link Commander needs to be started and the "WebUSBEnable" command needs to be executed:

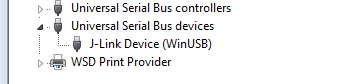

After power-cycling the J-Link OB, it will be listed as a WinUSB device in the device manager: