Difference between revisions of "ST STM32F4"

(→Option byte programming) |

(→QSPI Flash) |

||

| (6 intermediate revisions by 2 users not shown) | |||

| Line 3: | Line 3: | ||

__TOC__ |

__TOC__ |

||

| − | == |

+ | ==Flash Banks== |

| + | ===Internal Flash=== |

||

The following flash regions are supported by J-Link. |

The following flash regions are supported by J-Link. |

||

{| class="seggertable" |

{| class="seggertable" |

||

|- |

|- |

||

| − | ! Device |

+ | ! Device || Base address !! Size || J-Link Support |

|- |

|- |

||

| − | | STM32F4xxx8 || |

+ | | STM32F4xxx8 || 0x08000000 || style="text-align:center;"|64 KB || style="text-align:center;"| {{YES}} |

|- |

|- |

||

| − | | STM32F4xxxB || |

+ | | STM32F4xxxB || 0x08000000 || style="text-align:center;"|128 KB || style="text-align:center;"| {{YES}} |

|- |

|- |

||

| − | | STM32F4xxxC || |

+ | | STM32F4xxxC || 0x08000000 || style="text-align:center;"|256 KB || style="text-align:center;"| {{YES}} |

|- |

|- |

||

| − | | STM32F4xxxD || |

+ | | STM32F4xxxD || 0x08000000 || style="text-align:center;"|384 KB || style="text-align:center;"| {{YES}} |

|- |

|- |

||

| − | | STM32F4xxxE || |

+ | | STM32F4xxxE || 0x08000000 || style="text-align:center;"|512 KB || style="text-align:center;"| {{YES}} |

|- |

|- |

||

| − | | STM32F4xxxG || |

+ | | STM32F4xxxG || 0x08000000 || style="text-align:center;"|1024 KB|| style="text-align:center;"| {{YES}} |

|- |

|- |

||

| − | | STM32F4xxxH || |

+ | | STM32F4xxxH || 0x08000000 || style="text-align:center;"|1536 KB || style="text-align:center;"| {{YES}} |

|- |

|- |

||

| − | | STM32F4xxxI || |

+ | | STM32F4xxxI || 0x08000000 || style="text-align:center;"|2048 KB|| style="text-align:center;"| {{YES}} |

|} |

|} |

||

| + | |||

| + | ===QSPI Flash=== |

||

| + | QSPI flash programming requires special handling compared to internal flash. For more information about this, please see the [[QSPI Flash Programming Support | QSPI Flash Programming Support article]].<br> |

||

| + | |||

| + | Some ST STM32F4 device series come with a QUADSPI controller which allows memory mapped read accesses to any (Q)SPI flash, connected to the QUADSPI interface of the MCU. <br> |

||

| + | J-Link supports for the STM32F446/STM32F469 devices:<br> |

||

| + | *One single or quad SPI device connected to BK1<br> |

||

| + | Two single or quad SPI devices are not supported yet (dual mode).<br> |

||

| + | |||

| + | J-Link supports multiple pin configurations for STM32F4xx. The default loader is marked in '''bold'''. |

||

| + | |||

| + | |||

| + | {| class="seggertable" |

||

| + | |- |

||

| + | ! Device !! Base address !! Maximum size !! Supported pin configuration |

||

| + | |- |

||

| + | | STM32F412 || 0x90000000 || up to 64 MB || '''CLK@PB2_nCS@PG6_D0@PF8_D1@PF9_D2@PF7_D3@PF6''' |

||

| + | |- |

||

| + | | STM32F446 || 0x90000000 || up to 64 MB || '''CLK@PD3_nCS@PG6_D0@PF8_D1@PF9_D2@PF7_D3@PF6''' |

||

| + | |- |

||

| + | | STM32F469 || 0x90000000 || up to 64 MB || '''CLK@PF10_nCS@PB6_D0@PF8_D1@PF9_D2@PF7_D3@PF6''' |

||

| + | |} |

||

| + | For pin configuration, different from the one used in the example flash algorithm, please get in touch with SEGGER directly via our support system: https://www.segger.com/ticket/. |

||

== Reset == |

== Reset == |

||

| Line 30: | Line 54: | ||

== Debug specific == |

== Debug specific == |

||

| + | Please refer to the [[ST_STM32#Device_specific_connect | general STM32 article]] |

||

| − | * If no connection can be established the J-Link will try to connect to the device via a connect under reset. |

||

| − | * On connect, some DBGMCU registers will be written to |

||

| − | ** freeze the watchdogs during halt to prevent unintended resets while debugging. |

||

| − | ** prevent the debug connection from breaking after the CPU enters deepsleep. |

||

| − | * When closing the J-Link connection, the DBGMCU registers are reset. |

||

== Option byte programming == |

== Option byte programming == |

||

| Line 69: | Line 89: | ||

== Securing/unsecuring the device == |

== Securing/unsecuring the device == |

||

Please refer to the generic wiki-article: [[STM32#MCU_Security]] |

Please refer to the generic wiki-article: [[STM32#MCU_Security]] |

||

| − | |||

| − | == STM32F446xx (Q)SPI support == |

||

| − | The ST STM32F446xx device series comes with a QUADSPI controller which allows memory mapped read accesses to any (Q)SPI flash, connected to the Quad-SPI interface of the MCU. This allows the J-Link DLL to support flash programming through the Quad-SPI interface. Unfortunately, there is no generic way how to implement flash programming because the used pins to connect the SPI flash is not defined but different pins can be used for the same QUADSPI alternate function and therefore, for each configuration, a slightly different RAMCode (different pin initialization / flash size) is required. We have developed a flash algorithm, which allows to program any common (Q)SPI flash, connected to the Quad-SPI interface of the ST STM32F446 device. The flash algorithm is based on the Open Flash Loader concept so it can easily exchanged if a pin configuration, different from the one used in the example flash algorithm, is required. In such cases, please get in touch with SEGGER directly via our support system: https://www.segger.com/ticket/. |

||

| − | === Example implementation === |

||

| − | As described above, the reference flash algorithm is based on the Open Flash Loader and therefore needs to be added manually using a JLinkDevices.xml file. An example JLinkDevices.xml entry as well as the used pinout in the example flash algorithm is given below. This example assumes a Winbond W25Q16DV (2MB flash) connected to the Quad-SPI interface of the STM32F446xx. For further information regarding the Open Flash Loader and how to use the JLinkDevices.xml file, please refer to the J-Link User Manual (UM08001), chapter ''10 Open Flash Loader''. |

||

| − | ====Quad-SPI interface pins==== |

||

| − | The example algorithm uses the following port pins to interface the (Q)SPI flash. |

||

| − | {| class="seggertable" |

||

| − | |- |

||

| − | ! Alternate function !! Port / Pin |

||

| − | |- |

||

| − | | QUADSPI_BK1_IO0 || PF8 |

||

| − | |- |

||

| − | | QUADSPI_BK1_IO1 || PF9 |

||

| − | |- |

||

| − | | QUADSPI_BK1_IO2 || PE2 |

||

| − | |- |

||

| − | | QUADSPI_BK1_IO3 || PF6 |

||

| − | |- |

||

| − | | QUADSPI_CLK || PB2 |

||

| − | |- |

||

| − | | QUADSPI_BK1_NCS || PG6 |

||

| − | |} |

||

| − | ====JLinkDevices.xml==== |

||

| − | <Database> |

||

| − | <Device> |

||

| − | <ChipInfo Vendor="ST" Name="STM32F446ZE" WorkRAMAddr="0x20000000" WorkRAMSize="0x18000" Core="JLINK_CORE_CORTEX_M4" /> |

||

| − | <FlashBankInfo Name="Internal Flash" BaseAddr="0x90000000" MaxSize="0x200000" Loader="ST_STM32F446_Reference.elf" LoaderType="FLASH_ALGO_TYPE_OPEN" /> |

||

| − | </Device> |

||

| − | </Database> |

||

| − | *[[File:ST_STM32F446_QSPI_JLinkDevicesXML.zip]] |

||

| − | ====Flash algorithm (*.elf)==== |

||

| − | This file contains the program routines used by the J-Link DLL during flash programming. |

||

| − | *[[File:ST_STM32F446_QSPI_ReferenceFlashAlgorithm.zip]] |

||

| − | ====IAR example project==== |

||

| − | The example project contains a simple counter loop which is linked into the (Q)SPI flash memory region @ address 0x90000000. The project includes the JLinkDevices.xml file as well as the ST_STM32F446_Reference.elf. It runs out-of-the-box. Please note, that IAR EWARM must at least use the J-Link DLL version V6.01a, which supports the Open Flash Loader. |

||

| − | *[[File:ST_STM32F446_QSPI_IARV6405.zip]] |

||

| − | |||

| − | == STM32F469xx (Q)SPI support == |

||

| − | The ST STM32F469xx device series comes with a QUADSPI controller which allows memory mapped read accesses to any (Q)SPI flash, connected to the Quad-SPI interface of the MCU. This allows the J-Link DLL to support flash programming through the Quad-SPI interface. Unfortunately, there is no generic way how to implement flash programming because the used pins to connect the SPI flash is not defined but different pins can be used for the same QUADSPI alternate function and therefore, for each configuration, a slightly different RAMCode (different pin initialization / flash size) is required. We have developed a flash algorithm, which allows to program any common (Q)SPI flash, connected to the Quad-SPI interface of the ST STM32F469 device. The flash algorithm is based on the Open Flash Loader concept so it can easily exchanged if a pin configuration, different from the one used in the example flash algorithm, is required. In such cases, please get in touch with SEGGER directly via our support system: https://www.segger.com/ticket/. |

||

| − | === Example implementation === |

||

| − | As described above, the reference flash algorithm is based on the Open Flash Loader and therefore needs to be added manually using a JLinkDevices.xml file. An example JLinkDevices.xml entry as well as the used pinout in the example flash algorithm is given below. This example assumes a Winbond W25Q16DV (2MB flash) connected to the Quad-SPI interface of the STM32F469xx. For further information regarding the Open Flash Loader and how to use the JLinkDevices.xml file, please refer to the J-Link User Manual (UM08001), chapter ''10 Open Flash Loader''. |

||

| − | |||

| − | ====Quad-SPI interface pins==== |

||

| − | The example algorithm uses the following port pins (as used on the STM32F469I-DISCO board) to interface the (Q)SPI flash. |

||

| − | {| class="seggertable" |

||

| − | |- |

||

| − | ! Alternate function !! Port / Pin |

||

| − | |- |

||

| − | | QUADSPI_BK1_IO0 || PF8 |

||

| − | |- |

||

| − | | QUADSPI_BK1_IO1 || PF9 |

||

| − | |- |

||

| − | | QUADSPI_BK1_IO2 || PF7 |

||

| − | |- |

||

| − | | QUADSPI_BK1_IO3 || PF6 |

||

| − | |- |

||

| − | | QUADSPI_CLK || PF10 |

||

| − | |- |

||

| − | | QUADSPI_BK1_NCS || PB6 |

||

| − | |} |

||

| − | |||

| − | ====JLinkDevices.xml==== |

||

| − | <Database> |

||

| − | <Device> |

||

| − | <ChipInfo Vendor="ST" Name="STM32F469NI" Core="JLINK_CORE_CORTEX_M4" /> |

||

| − | <FlashBankInfo Name="QSPI Flash" BaseAddr="0x90000000" MaxSize="0x01000000" Loader="ST_STM32F469I_Disco_QSPI.elf" LoaderType="FLASH_ALGO_TYPE_OPEN" /> |

||

| − | </Device> |

||

| − | </Database> |

||

| − | *[[File:ST_STM32F469I_Disco_QSPI_JLinkDevicesXML.zip]] |

||

| − | |||

| − | ====Flash algorithm (*.elf)==== |

||

| − | This file contains the program routines used by the J-Link DLL during flash programming. |

||

| − | *[[File:ST_STM32F469I_Disco_QSPI_ReferenceFlashAlgorithm.zip]] |

||

| − | ====IAR example project==== |

||

| − | The example project contains a simple counter loop which is linked into the (Q)SPI flash memory region @ address 0x90000000. The project includes the JLinkDevices.xml file as well as the ST_STM32F469I_Disco_QSPI.elf. It runs out-of-the-box. Please note, that IAR EWARM must at least use the J-Link DLL version V6.01a, which supports the Open Flash Loader. |

||

| − | *[[File:ST_STM32F469I_Disco_QSPI_IARV6405.zip]] |

||

== RTT == |

== RTT == |

||

Latest revision as of 10:51, 2 April 2024

This article describes device specifics of the ST STM32F4 series devices. The STM32F4 devices are Cortex-M0 based MCUs with low-power functionality.

Contents

Flash Banks

Internal Flash

The following flash regions are supported by J-Link.

| Device | Base address | Size | J-Link Support |

|---|---|---|---|

| STM32F4xxx8 | 0x08000000 | 64 KB | |

| STM32F4xxxB | 0x08000000 | 128 KB | |

| STM32F4xxxC | 0x08000000 | 256 KB | |

| STM32F4xxxD | 0x08000000 | 384 KB | |

| STM32F4xxxE | 0x08000000 | 512 KB | |

| STM32F4xxxG | 0x08000000 | 1024 KB | |

| STM32F4xxxH | 0x08000000 | 1536 KB | |

| STM32F4xxxI | 0x08000000 | 2048 KB |

QSPI Flash

QSPI flash programming requires special handling compared to internal flash. For more information about this, please see the QSPI Flash Programming Support article.

Some ST STM32F4 device series come with a QUADSPI controller which allows memory mapped read accesses to any (Q)SPI flash, connected to the QUADSPI interface of the MCU.

J-Link supports for the STM32F446/STM32F469 devices:

- One single or quad SPI device connected to BK1

Two single or quad SPI devices are not supported yet (dual mode).

J-Link supports multiple pin configurations for STM32F4xx. The default loader is marked in bold.

| Device | Base address | Maximum size | Supported pin configuration |

|---|---|---|---|

| STM32F412 | 0x90000000 | up to 64 MB | CLK@PB2_nCS@PG6_D0@PF8_D1@PF9_D2@PF7_D3@PF6 |

| STM32F446 | 0x90000000 | up to 64 MB | CLK@PD3_nCS@PG6_D0@PF8_D1@PF9_D2@PF7_D3@PF6 |

| STM32F469 | 0x90000000 | up to 64 MB | CLK@PF10_nCS@PB6_D0@PF8_D1@PF9_D2@PF7_D3@PF6 |

For pin configuration, different from the one used in the example flash algorithm, please get in touch with SEGGER directly via our support system: https://www.segger.com/ticket/.

Reset

For the STM32F4 devices, the Cortex-M default reset strategy is used.

Debug specific

Please refer to the general STM32 article

Option byte programming

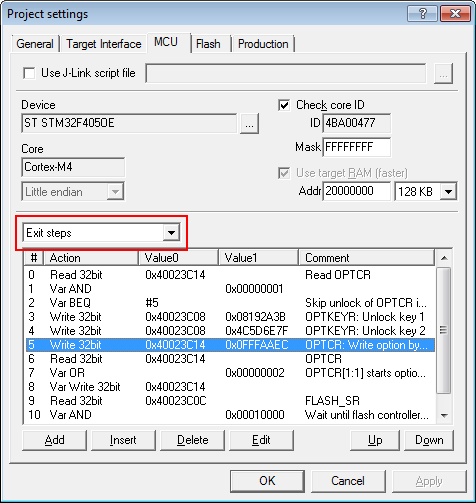

The STM32F4 series devices provide some option bytes which allow some "permanent" configuration as well as readout protection for the device. Unfortunately, the option bytes become effective immediately when programmed. This means when enabling the read protection of the device via option bytes, the programmer will immediately lose the access to the flash, without any possibility to verify the complete flash operation. Therefore, the option bytes cannot be programmed as part of the flash image. The sequence, to program the option bytes consists of multiple read / write accesses to special function registers of the STM32F4 MCU.

Via J-Flash / Flasher ARM

The sequence to program the option bytes, needs to be added to the exit-steps of the J-Flash project. The exit steps will be executed at the end of an successful auto-programming process (Target -> Auto). J-Flash comes with an example project for the STM32F405OE which contains the option byte programming sequence (File:STM32F405OE OptBytes.jflash). This sequence applies for all STM32F2 / F4 devices since they are compatible regarding option byte programming and can be adapted to fit custom requirements. The option byte values are transmitted in exit step # 5, which writes the OPTCR.

Modification example (seting WDG_SW byte and read protection bit)

As mentioned above, the option bytes can be customized by changing step # 5 of the Exit steps above.

Necessary changes of "Step 5" in "Data" section:

| Value | Effect |

|---|---|

| 0x0FFFAABC | Read protection level 0, WDG_SW set to Hardware independent watchdog |

| 0x0FFFAAEC | Read protection level 0, WDG_SW set to Software independent watchdog |

| 0x0FFFBBBC | Read protection level 1, WDG_SW set to Hardware independent watchdog |

| 0x0FFFBBEC | Read protection level 1, WDG_SW set to Software independent watchdog |

| 0x0FFFCCBC | Read protection level 2, WDG_SW set to Hardware independent watchdog |

| 0x0FFFCCEC | Read protection level 2, WDG_SW set to Software independent watchdog |

- For STM32F42xxx and STM32F43xxx devices, bit 4 is used for setting the single or dual bank flash memory option. In this example the default case (single bank flash memory) was selected.

- After changing WDG_SW, the device must be reset for the changes to take effect.

Securing/unsecuring the device

Please refer to the generic wiki-article: STM32#MCU_Security

RTT

SEGGER's RTT can be used with a J-Link connected to a STM32F4 target device.

Sample project

For a sample Embedded Studio project, refer to the following .zip archive:

ST_STM32F446ZE_NUCLEO_RTT.zip

The above project was tested with the following setup:

| Target device | STM32F446ZE |

| Evalboard | NUCLEO-F446ZE (ST) |

| J-Link software version | V6.51b |

| Embedded Studio version | V4.18 |