Difference between revisions of "ST STM32U5"

(→QSPI support) |

(→TrustZone) |

||

| (41 intermediate revisions by 4 users not shown) | |||

| Line 1: | Line 1: | ||

| + | The '''ST STM32U5 series''' are 32-bit ultra low power microcontrollers based on the ARM Cortex-M33 processor. |

||

__TOC__ |

__TOC__ |

||

| − | The ST STM32U5 series are 32-bit ultra low power microcontrollers based on the ARM Cortex-M33 processor. |

||

| − | ==Device family== |

||

| + | |||

| − | The STM32U5 device family consists of several subfamilies: STM32U57xxx, STM32U58xxx, STM32U59xxx and STM32U5Axxx. |

||

| + | ==Flash Banks== |

||

| − | {| class="wikitable" |

||

| + | ===Internal Flash=== |

||

| + | {| class="seggertable" |

||

|- |

|- |

||

| + | ! Flash Bank || Base address !! Size || J-Link Support |

||

| − | ! STM32U57xxx !! STM32U58xxx !! STM32U59xxx !! STM32U5Axxx |

||

|- |

|- |

||

| + | | Non-Secure Internal Flash || 0x08000000 || style="text-align:center;"|Up to 4MB || style="text-align:center;"| {{YES}} |

||

| − | | STM32U575AI || STM32U585AI || STM32U595ZJ || STM32U5A5ZJ |

||

|- |

|- |

||

| + | | Secure Internal Flash || 0x0C000000 || style="text-align:center;"|Up to 4MB || style="text-align:center;"| {{YES}} |

||

| − | | STM32U575CI || STM32U585CI || STM32U599BJ || STM32U5A9BJ |

||

|- |

|- |

||

| + | | User Option || 0x40022040 || style="text-align:center;"|48B || style="text-align:center;"| {{NO}} |

||

| − | | STM32U575OI || STM32U585OI || STM32U599NJ || STM32U5A9NJ |

||

| + | |} |

||

| + | |||

| + | |||

| + | ===QSPI Flash=== |

||

| + | QSPI flash programming requires special handling compared to internal flash. For more information about this, please see the [[QSPI Flash Programming Support | QSPI Flash Programming Support article]].<br> |

||

| + | |||

| + | |||

| + | The ST STM32U5 device series comes with OCTASPI controller which allows memory mapped read accesses to any (Q)SPI flash, connected to the Octa-SPI interface of the MCU. |

||

| + | J-Link supports for the STM32U5: |

||

| + | *One single or quad SPI device connected to D0 to D3 |

||

| + | *Two single or quad SPI devices connected to D0 to D7 (dual mode) |

||

| + | Octo SPI is not supported yet. |

||

| + | |||

| + | Some STM32U5 sub-family devices additionally come with HSPI controller which also allow memory mapped read access to any (Q)SPI flash, connected to the Hexadeca-SPI interface of the MCU. |

||

| + | J-Link support for the STM32U5Gxxx: |

||

| + | *One single or quad SPI device connected to HSPI1 GPIOs on Port H. |

||

| + | Other SPI modes are not supported yet. |

||

| + | |||

| + | J-Link supports multiple pin configurations for STM32U5. The default loader is marked in '''bold'''. |

||

| + | |||

| + | {| class="seggertable" |

||

|- |

|- |

||

| + | ! Device !! Base address !! Maximum size !! Supported pin configuration |

||

| − | | STM32U575QI || STM32U585QI || || |

||

|- |

|- |

||

| + | | |

||

| − | | STM32U575RI || STM32U585RI || || |

||

| + | *STM32U575 |

||

| + | *STM32U585 |

||

| + | *STM32U5A9 |

||

| + | || 0x90000000 || up to 64 MB || |

||

| + | *'''CLK@PF4_nCS@PI5_D0@PF0_D1@PF1_D2@PF2_D3@PF3''' |

||

| + | *CLK@PF10_nCS@PA2_D0@PF8_D1@PF9_D2@PF7_D3@PF6 |

||

| + | *CLK@PH6_nCS@PI5_D0@PI3_D1@PI2_D2@PI1_D3@PH8 |

||

|- |

|- |

||

| + | | |

||

| − | | STM32U575VI || STM32U585VI || || |

||

| + | *STM32U5G9 |

||

| + | || 0xA0000000 || up to 64 MB || |

||

| + | *'''CLK@PI3_nCS@PH9_D0@PH10_D1@PH11_D2@PH12_D3@PH13_D4@NA_D5@NA_D6@NA_D7@NA''' |

||

| + | |} |

||

| + | |||

| + | |||

| + | For pin configuration, different from the one used in the example flash algorithm, please get in touch with SEGGER directly via our support system: https://www.segger.com/ticket/. |

||

| + | |||

| + | == Device family == |

||

| + | The STM32U5 device family consists of several subfamilies: |

||

| + | |||

| + | {| class="seggertable" |

||

|- |

|- |

||

| + | ! Subfamily || style="text-align:center;"|Flash size || Remarks |

||

| − | | STM32U575ZI || STM32U585ZI || || |

||

|- |

|- |

||

| + | | STM32U535 || style="text-align:center;"|128KB to 512KB|| QSPI not supported yet |

||

| − | | STM32U575AG || STM32U585AG || || |

||

|- |

|- |

||

| + | | STM32U545 || style="text-align:center;"|512KB || QSPI not supported yet |

||

| − | | STM32U575CG || STM32U585CG || || |

||

|- |

|- |

||

| + | | STM32U575 || style="text-align:center;"|1MB to 2MB|| |

||

| − | | STM32U575OG || STM32U585OG || || |

||

|- |

|- |

||

| + | | STM32U585 || style="text-align:center;"|2MB|| |

||

| − | | STM32U575QG || STM32U585QG || || |

||

|- |

|- |

||

| + | | STM32U599 || style="text-align:center;"|2MB to 4 MB|| |

||

| − | | STM32U575RG || STM32U585RG || || |

||

| − | |- |

||

| − | | STM32U575VG || STM32U585VG || || |

||

| − | |- |

||

| − | | STM32U575ZG || STM32U585ZG || || |

||

|- |

|- |

||

| + | | STM32UA9 || style="text-align:center;"|4 MB || |

||

|} |

|} |

||

| + | ==Watchdog Handling== |

||

| − | ==On-Chip Memory Regions== |

||

| + | *The device has a watchdog IWDG. |

||

| − | The internal flash consists of up to 4MiB of memory. |

||

| + | *The watchdog is fed during flash programming and stopped during halt. |

||

| + | == Reset == |

||

| − | {| class="wikitable" |

||

| + | For the STM32U5 devices, the [[J-Link_Reset_Strategies#Type_0:_Normal | Cortex-M default reset strategy]] is used. |

||

| − | |- |

||

| − | ! Device !! Flash size (MiB) !! Start address !! End address |

||

| − | |- |

||

| − | | STM32U5xxxG || 1 || 0x08000000 || 0x080FFFFF |

||

| − | |- |

||

| − | | STM32U5xxxI || 2 || 0x08000000 || 0x081FFFFF |

||

| − | |- |

||

| − | | STM32U5xxxJ || 4 || 0x08000000 || 0x083FFFFF |

||

| − | |} |

||

| − | == |

+ | == Debug specific == |

| + | Please refer to the [[ST_STM32#Device_specific_connect | generic STM32 article]]. |

||

| − | The ST STM32U5xxx device series comes with a OCTASPI controller which allows memory mapped read accesses to any (Q)SPI flash, connected to the Octa-SPI interface of the MCU. This allows the J-Link DLL to support flash programming through the Octa-SPI interface. Unfortunately, there is no generic way how to implement flash programming because the pins used to connect the SPI flash are not defined. Different pins can be used for the same OCTASPI alternate function and therefore, for each configuration, a slightly different RAMCode (different pin initialization / flash size) is required. Our flash algorithms are based on the pin configurations used on the official evaluation boards. For pin configuration, different from the one used in the example flash algorithm, please get in touch with SEGGER directly via our support system: https://www.segger.com/ticket/. |

||

| + | == Option byte programming == |

||

| − | For further information regarding this as well as the flash algorithm, please refer to the following pages: |

||

| + | Direct option byte programming is not (yet) implemented for the ST STM32U5. |

||

| − | * '''STM32U5xx:''' [https://wiki.segger.com/STM32U585I_Discovery STM32U585 Discovery] |

||

| + | However, the same method used to lock/unlock the devices can be used as described in [[#Securing/unsecuring_the_device|Securing/unsecuring the device]] can be used to adjust any option bytes. |

||

| + | == Securing/unsecuring the device == |

||

| − | ==Reset== |

||

| + | Please refer to the [[ST_STM32#MCU_Security | generic STM32 article]]. |

||

| − | No special reset is required. |

||

== TrustZone == |

== TrustZone == |

||

| + | The TrustZone feature may be used for the STM32U5 devices, however, there are a couple of limitations that have to be kept in mind: |

||

| + | * Flash programming with TrustZone enabled (TZEN = 1) is generally supported when RDP level is 0 or 0.5. |

||

| + | * For programming RDP level 0.5 a RAMless flashloader has to be used due to a technical limitation.<br>'''Please note''' that a significantly lower programming speed has to be expected when using the RAMless flashloader. |

||

| + | * The J-Link software can not determine whether to use the RAMCode or RAMless flashloader, so it is user responsibility to select the correct flashloader beforehand, by adding "_RAMLess" to the device name, e.g. use "STM32U599NJ_RAMLess" instead of "STM32U599NJ". |

||

| + | === Clearing TZEN via J-Link === |

||

| − | Flash programming with TrustZone enabled (TZEN = 1) is supported. |

||

| + | To disable TrustZone via debug probe, an RDP regression has to be performed (RDP Level 1 => 0). |

||

| + | However if TZEN == 1 and RDP Level == 1, a debug connection can only be established while the device is executing non-secure code. |

||

| + | To make sure that the device is executing non-secure code, it can be forced to boot in ST bootloader mode.<br> |

||

| + | The following [[J-Link Script file]] can be used to automatically disable TrustZone on connect: |

||

| + | * [[Media:ST_STM32U5_DisableTZEN.pex | ST_STM32U5_DisableTZEN.pex]] |

||

| + | {{Note|1=Regressing RDP from Level 1 to 0 will trigger a mass erase of the device.}} |

||

| + | ==Evaluation Boards== |

||

| − | RDP level 0 and 0.5 is also supported. The RAMCode is only usable with RDP level 0, for RDP level 0.5 a RAMless flashloader has to be used. This is a technical limitation. The J-Link software is not able to decide at runtime when to use the RAMCode or RAMless flashloader. If you want to use the RAMless flashloader for RDP 0.5, you have to add "_RAMLess" to the device name, e.g. use "STM32U599NJ_RAMLess" instead of "STM32U599NJ". |

||

| + | *ST STM32U575I-EV evaluation board: https://wiki.segger.com/ST_STM32U575I-EV |

||

| − | Please note that a significantly lower programming speed has to be expected with the RAMless flashloader. |

||

| + | *ST STM32U599J-DK evaluation board: https://wiki.segger.com/ST_STM32U599J-DK |

||

| + | *ST STM32U5A9NJ evaluation board: https://wiki.segger.com/ST_STM32U5A9NJ |

||

| + | *ST STM32U585 evaluation board: https://wiki.segger.com/ST_STM32U585 |

||

| + | *ST STM32U5A9NJ evaluation board: https://wiki.segger.com/ST_STM32U5A9NJ |

||

| + | *ST NUCLEO-U545R-Q evaluation board: https://wiki.segger.com/ST_NUCLEO-U545R-Q |

||

| + | *ST NUCLEO-U575ZI-Q evaluation board: https://wiki.segger.com/ST_NUCLEO-U575ZI-Q |

||

==Example Application== |

==Example Application== |

||

| + | *ST STM32U575I-EV evaluation board: https://wiki.segger.com/ST_STM32U575I-EV#Example_Project |

||

| + | *ST STM32U599J-DK evaluation board: https://wiki.segger.com/ST_STM32U599J-DK#Example_Project |

||

| + | *ST STM32U5A9NJ evaluation board: https://wiki.segger.com/ST_STM32U5A9NJ#Example_Project |

||

| + | *ST STM32U585 evaluation board: https://wiki.segger.com/ST_STM32U585#Example_Project |

||

| + | *ST STM32U5A9NJ evaluation board: https://wiki.segger.com/ST_STM32U5A9NJ#Example_Project |

||

| + | *ST NUCLEO-U545R-Q evaluation board: https://wiki.segger.com/ST_NUCLEO-U545R-Q#Example_Project |

||

| + | *ST NUCLEO-U575ZI-Q evaluation board: https://wiki.segger.com/ST_NUCLEO-U575ZI-Q#Example_Project |

||

| + | |||

| + | == Example Application == |

||

The following example project was created with the SEGGER Embedded Studio project wizard and should run out-of-the-box on any ST STM32U5xxxx device. It is a simple for loop incrementing the integer i. The application is linked into the internal flash.<br> |

The following example project was created with the SEGGER Embedded Studio project wizard and should run out-of-the-box on any ST STM32U5xxxx device. It is a simple for loop incrementing the integer i. The application is linked into the internal flash.<br> |

||

'''SETUP''' |

'''SETUP''' |

||

| Line 75: | Line 132: | ||

*Hardware: Socket board with ST STM32U5 mounted |

*Hardware: Socket board with ST STM32U5 mounted |

||

*Link: [[File:ST_STM32U5xxxx_TestProject_ES_V534.zip]] |

*Link: [[File:ST_STM32U5xxxx_TestProject_ES_V534.zip]] |

||

| + | |||

| + | == Tracing on ST STM32U5 == |

||

| + | === Tracing on ST STM32U575 === |

||

| + | The following project has been tested with the minimum requirements mentioned and a ''ST STM32U575I-EVAL'' evaluation board. |

||

| + | |||

| + | ==== Minimum requirements ==== |

||

| + | In order to use trace on the ST STM32U575 MCU devices, the following minimum requirements have to be met: |

||

| + | * J-Link software version V7.66d or later |

||

| + | * Ozone V3.26b or later (if streaming trace and / or the sample project from below shall be used) |

||

| + | * J-Trace PRO for Cortex-M HW version V1.0 or later for streaming trace |

||

| + | |||

| + | To rebuild the project our IDE Embedded Studio can be used. The recommended version to rebuild the projects is V6.30. But the examples are all prebuild and work out-of-the box with Ozone, so rebuilding is not necessary. |

||

| + | |||

| + | ==== Streaming trace ==== |

||

| + | '''Example Project:''' [[Media:ST_STM32U575I_EV_TraceSample.zip | ST_STM32U575I_EV_TraceSample.zip]] |

||

| + | |||

| + | '''Note:''' The example is shipped with a compiled .JLinkScriptfile, should you need the original source, please get in touch with SEGGER directly via our support system: https://www.segger.com/ticket/. |

||

| + | |||

| + | To create your own .JLinkScriptfile you can use the following guide as reference: [[How_to_configure_JLinkScript_files_to_enable_tracing]] |

||

| + | |||

| + | ==== Tested Hardware ==== |

||

| + | [[File:STM32U575I-EVAL.jpg|none|thumb|ST STM32U575I-EVAL]] |

||

| + | |||

| + | ==== Reference trace signal quality ==== |

||

| + | The following pictures show oscilloscope measurements of trace signals output by the "Tested Hardware" using the example project. |

||

| + | All measurements have been performed using a Agilent InfiniiVision DSO7034B 350 MHz 2GSa/s oscilloscope and 1156A 1.5 GHz Active Probes. |

||

| + | If your trace signals look similar on your trace hardware, chances are good that tracing will work out-of-the-box using the example project. |

||

| + | More information about correct trace timing can be found at the following [https://www.segger.com/products/debug-probes/j-trace/technology/setting-up-trace/ website]. |

||

| + | |||

| + | ===== Rise time ===== |

||

| + | The rise time of a signal shows the time needed for a signal to rise from logical 0 to logical 1. |

||

| + | For this the values at 10% and 90% of the expected voltage level get used as markers. |

||

| + | The following picture shows such a measurement for the trace clock signal. |

||

| + | [[File:STM32U575_Risetime_TCLK.png|none|thumb|TCLK rise time]] |

||

| + | |||

| + | ===== Setup time ===== |

||

| + | The setup time shows the relative setup time between a trace data signal and trace clock. |

||

| + | The measurement markers are set at 50% of the expected voltage level respectively. |

||

| + | The following picture shows such a measurement for the trace data signal 0 relative to the trace clock signal. |

||

| + | [[File:STM32U575_Setuptime_TD0.png|none|thumb|TD0 setup time]] |

||

Latest revision as of 12:53, 18 March 2024

The ST STM32U5 series are 32-bit ultra low power microcontrollers based on the ARM Cortex-M33 processor.

Contents

Flash Banks

Internal Flash

| Flash Bank | Base address | Size | J-Link Support |

|---|---|---|---|

| Non-Secure Internal Flash | 0x08000000 | Up to 4MB | |

| Secure Internal Flash | 0x0C000000 | Up to 4MB | |

| User Option | 0x40022040 | 48B |

QSPI Flash

QSPI flash programming requires special handling compared to internal flash. For more information about this, please see the QSPI Flash Programming Support article.

The ST STM32U5 device series comes with OCTASPI controller which allows memory mapped read accesses to any (Q)SPI flash, connected to the Octa-SPI interface of the MCU.

J-Link supports for the STM32U5:

- One single or quad SPI device connected to D0 to D3

- Two single or quad SPI devices connected to D0 to D7 (dual mode)

Octo SPI is not supported yet.

Some STM32U5 sub-family devices additionally come with HSPI controller which also allow memory mapped read access to any (Q)SPI flash, connected to the Hexadeca-SPI interface of the MCU. J-Link support for the STM32U5Gxxx:

- One single or quad SPI device connected to HSPI1 GPIOs on Port H.

Other SPI modes are not supported yet.

J-Link supports multiple pin configurations for STM32U5. The default loader is marked in bold.

| Device | Base address | Maximum size | Supported pin configuration |

|---|---|---|---|

|

0x90000000 | up to 64 MB |

|

|

0xA0000000 | up to 64 MB |

|

For pin configuration, different from the one used in the example flash algorithm, please get in touch with SEGGER directly via our support system: https://www.segger.com/ticket/.

Device family

The STM32U5 device family consists of several subfamilies:

| Subfamily | Flash size | Remarks |

|---|---|---|

| STM32U535 | 128KB to 512KB | QSPI not supported yet |

| STM32U545 | 512KB | QSPI not supported yet |

| STM32U575 | 1MB to 2MB | |

| STM32U585 | 2MB | |

| STM32U599 | 2MB to 4 MB | |

| STM32UA9 | 4 MB |

Watchdog Handling

- The device has a watchdog IWDG.

- The watchdog is fed during flash programming and stopped during halt.

Reset

For the STM32U5 devices, the Cortex-M default reset strategy is used.

Debug specific

Please refer to the generic STM32 article.

Option byte programming

Direct option byte programming is not (yet) implemented for the ST STM32U5. However, the same method used to lock/unlock the devices can be used as described in Securing/unsecuring the device can be used to adjust any option bytes.

Securing/unsecuring the device

Please refer to the generic STM32 article.

TrustZone

The TrustZone feature may be used for the STM32U5 devices, however, there are a couple of limitations that have to be kept in mind:

- Flash programming with TrustZone enabled (TZEN = 1) is generally supported when RDP level is 0 or 0.5.

- For programming RDP level 0.5 a RAMless flashloader has to be used due to a technical limitation.

Please note that a significantly lower programming speed has to be expected when using the RAMless flashloader. - The J-Link software can not determine whether to use the RAMCode or RAMless flashloader, so it is user responsibility to select the correct flashloader beforehand, by adding "_RAMLess" to the device name, e.g. use "STM32U599NJ_RAMLess" instead of "STM32U599NJ".

Clearing TZEN via J-Link

To disable TrustZone via debug probe, an RDP regression has to be performed (RDP Level 1 => 0).

However if TZEN == 1 and RDP Level == 1, a debug connection can only be established while the device is executing non-secure code.

To make sure that the device is executing non-secure code, it can be forced to boot in ST bootloader mode.

The following J-Link Script file can be used to automatically disable TrustZone on connect:

Regressing RDP from Level 1 to 0 will trigger a mass erase of the device.

Evaluation Boards

- ST STM32U575I-EV evaluation board: https://wiki.segger.com/ST_STM32U575I-EV

- ST STM32U599J-DK evaluation board: https://wiki.segger.com/ST_STM32U599J-DK

- ST STM32U5A9NJ evaluation board: https://wiki.segger.com/ST_STM32U5A9NJ

- ST STM32U585 evaluation board: https://wiki.segger.com/ST_STM32U585

- ST STM32U5A9NJ evaluation board: https://wiki.segger.com/ST_STM32U5A9NJ

- ST NUCLEO-U545R-Q evaluation board: https://wiki.segger.com/ST_NUCLEO-U545R-Q

- ST NUCLEO-U575ZI-Q evaluation board: https://wiki.segger.com/ST_NUCLEO-U575ZI-Q

Example Application

- ST STM32U575I-EV evaluation board: https://wiki.segger.com/ST_STM32U575I-EV#Example_Project

- ST STM32U599J-DK evaluation board: https://wiki.segger.com/ST_STM32U599J-DK#Example_Project

- ST STM32U5A9NJ evaluation board: https://wiki.segger.com/ST_STM32U5A9NJ#Example_Project

- ST STM32U585 evaluation board: https://wiki.segger.com/ST_STM32U585#Example_Project

- ST STM32U5A9NJ evaluation board: https://wiki.segger.com/ST_STM32U5A9NJ#Example_Project

- ST NUCLEO-U545R-Q evaluation board: https://wiki.segger.com/ST_NUCLEO-U545R-Q#Example_Project

- ST NUCLEO-U575ZI-Q evaluation board: https://wiki.segger.com/ST_NUCLEO-U575ZI-Q#Example_Project

Example Application

The following example project was created with the SEGGER Embedded Studio project wizard and should run out-of-the-box on any ST STM32U5xxxx device. It is a simple for loop incrementing the integer i. The application is linked into the internal flash.

SETUP

- J-Link software: V6.99a

- Embedded Studio: V5.34 (or later)

- Hardware: Socket board with ST STM32U5 mounted

- Link: File:ST STM32U5xxxx TestProject ES V534.zip

Tracing on ST STM32U5

Tracing on ST STM32U575

The following project has been tested with the minimum requirements mentioned and a ST STM32U575I-EVAL evaluation board.

Minimum requirements

In order to use trace on the ST STM32U575 MCU devices, the following minimum requirements have to be met:

- J-Link software version V7.66d or later

- Ozone V3.26b or later (if streaming trace and / or the sample project from below shall be used)

- J-Trace PRO for Cortex-M HW version V1.0 or later for streaming trace

To rebuild the project our IDE Embedded Studio can be used. The recommended version to rebuild the projects is V6.30. But the examples are all prebuild and work out-of-the box with Ozone, so rebuilding is not necessary.

Streaming trace

Example Project: ST_STM32U575I_EV_TraceSample.zip

Note: The example is shipped with a compiled .JLinkScriptfile, should you need the original source, please get in touch with SEGGER directly via our support system: https://www.segger.com/ticket/.

To create your own .JLinkScriptfile you can use the following guide as reference: How_to_configure_JLinkScript_files_to_enable_tracing

Tested Hardware

Reference trace signal quality

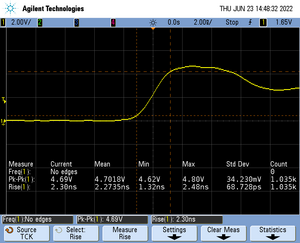

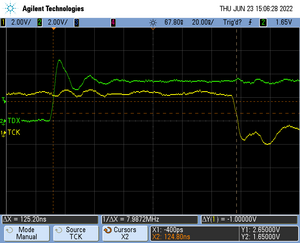

The following pictures show oscilloscope measurements of trace signals output by the "Tested Hardware" using the example project. All measurements have been performed using a Agilent InfiniiVision DSO7034B 350 MHz 2GSa/s oscilloscope and 1156A 1.5 GHz Active Probes. If your trace signals look similar on your trace hardware, chances are good that tracing will work out-of-the-box using the example project. More information about correct trace timing can be found at the following website.

Rise time

The rise time of a signal shows the time needed for a signal to rise from logical 0 to logical 1. For this the values at 10% and 90% of the expected voltage level get used as markers. The following picture shows such a measurement for the trace clock signal.

Setup time

The setup time shows the relative setup time between a trace data signal and trace clock. The measurement markers are set at 50% of the expected voltage level respectively. The following picture shows such a measurement for the trace data signal 0 relative to the trace clock signal.