Difference between revisions of "SiFive Arty FPGA Dev Kit"

(→Debugging in FreedomStudio) |

(→Debugging in FreedomStudio) |

||

| Line 70: | Line 70: | ||

'''Before continuing, make sure that you have J-Link software package V6.20c or later installed''': [https://www.segger.com/downloads/jlink/ Download J-Link software package] |

'''Before continuing, make sure that you have J-Link software package V6.20c or later installed''': [https://www.segger.com/downloads/jlink/ Download J-Link software package] |

||

| + | |||

| + | Pics: |

||

| + | |||

| + | [[File:FreedomStudio_Debug.png]] |

||

| + | [[File:FreedomStudio_Debug_Debugger.png]] |

||

| + | [[File:FreedomStudio_Debug_Startup.png]] |

||

| + | [[File:FreedomStudio_NewDebugConfig.png]] |

||

| + | |||

TBD |

TBD |

||

Revision as of 15:44, 26 September 2017

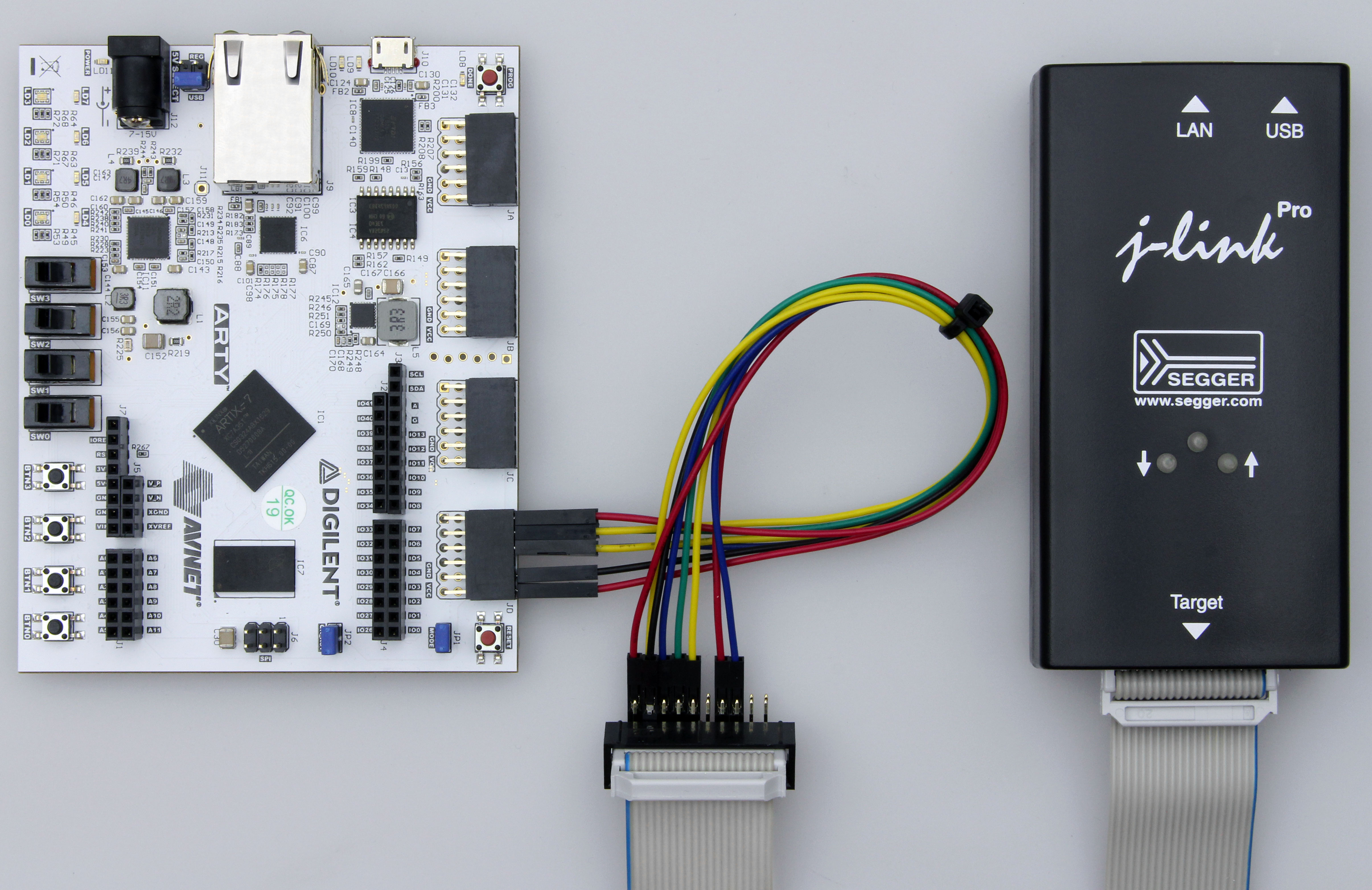

This article describes specifics for the SiFive Arty FPGA Dev Kit.

Preparing for J-Link

The SiFive Arty FPGA Dev Kit does not come with a standard debug connector but populates the debug JTAG signals on a custom connector. Therefore, it needs to be manually wired in case J-Link shall be connected to it.

In the following, it is described how the pins of connector JD on the ARTY board needs to be wired to J-Link. All pins of the J-Link side refer to the standard 0.1" 20-pin connector of J-Link.

| Pin ARTY | Pin J-Link | Description |

|---|---|---|

| 1 | 13 | TDO |

| 2 | 3 | nTRST |

| 3 | 9 | TCK |

| 7 | 5 | TDI |

| 8 | 7 | TMS |

| 9 | 15 | nRESET |

| 11 | 4 | GND |

| 12 | 1 | VTref |

Note: The pins on the JD connector are numbered as follows:

| 6 | 5 | 4 | 3 | 2 | 1 |

| 12 | 11 | 10 | 9 | 8 | 7 |

Debugging in FreedomStudio

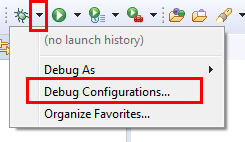

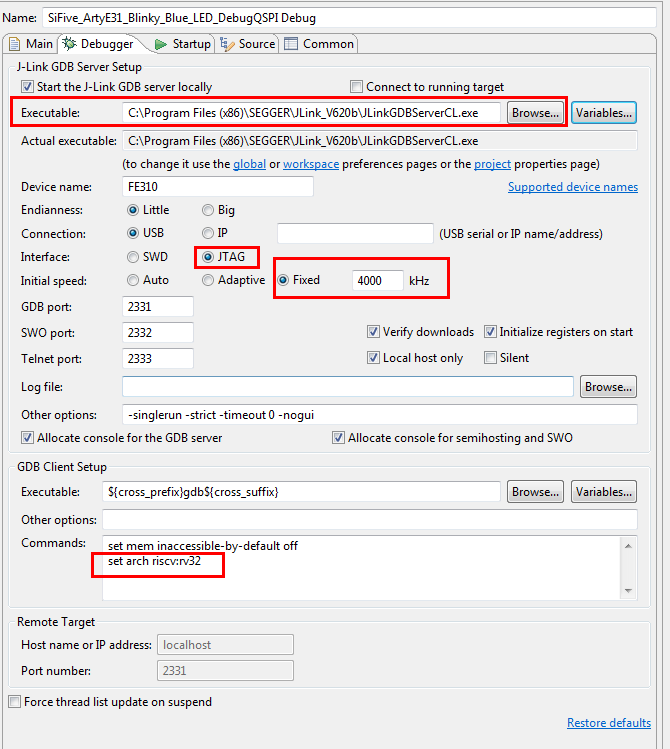

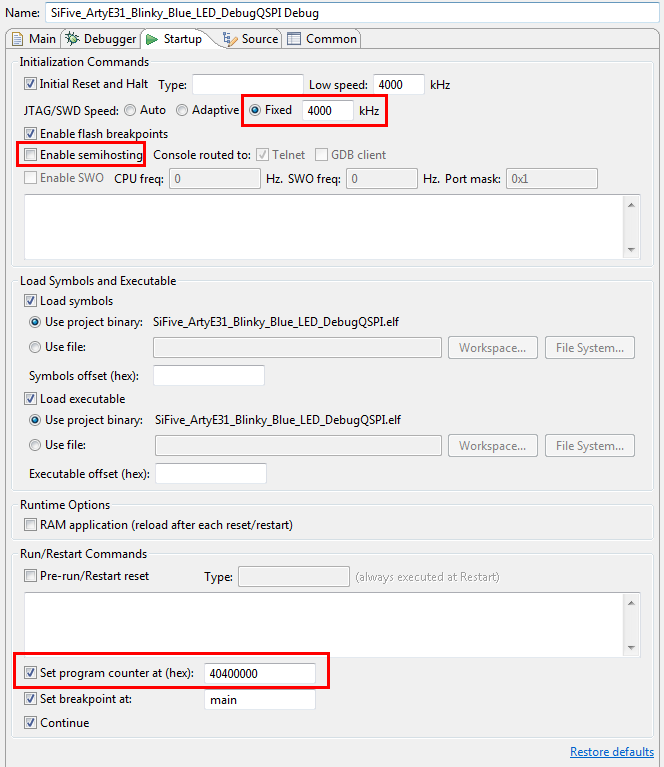

Before continuing, make sure that you have J-Link software package V6.20c or later installed: Download J-Link software package

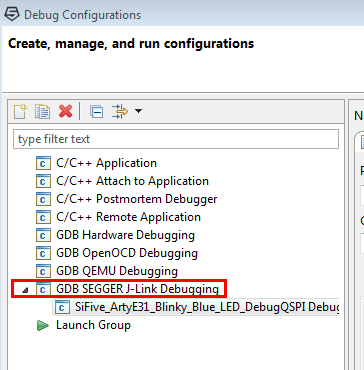

Pics:

TBD

Example projects for FreedomStudio

TBD