SiFive E31

The SiFive E31 is a 32-bit (RV32) core of the SiFive E3 series cores, designed by SiFive.

Contents

Minimum required J-Link software version

The E31 and E31ARTY device selection are supported by J-Link software.

E31ARTY device selection

The E31ARTY is a special device that can be selected for J-Link. It selects the standard SiFive E31 that is implemented for the sample bitstream as part of the SiFive E31 Standard Core Dev Kit. Device specifics include:

- Memory map

- Flash banks

As the E31 is a customizable core, the E31ARTY selection may not be appropriate for customized cores but for the standard one running on the ARTY-100T FPGA evaluation board only.

Tracing on SiFive E31 cores

This section describes how to get started with trace on the SiFive E31 core MCUs. This section assumes that there is already a basic knowledge about trace in general (what is trace, what different implementations of trace are there, etc.). If this is not the case, we recommend to read Trace chapter in the J-Link User Manual (UM08001).

Note:

- The sample projects come with a pre-configured project file for Ozone that runs out-of-the box.

- The following sample project is designed to be used with J-Trace PRO for streaming trace, J-Link Plus for buffer tracing and Ozone.

- In order to rebuild the sample project, SEGGER Embedded Studio can be used.

Minimum requirements

In order to use trace on the SiFive E31 core MCUs, the following minimum requirements have to be met:

- J-Link software version V7.80b or later

- Ozone V3.26h or later (if the sample project from below shall be used)

- J-Trace PRO for RISC-V HW version V3.0 or later for streaming trace

- J-Link Plus V11 or later for buffer trace

- The bitstream used in the FPGA board must support SiFive Nexus BTM tracing

To rebuild the project our IDE Embedded Studio can be used. The recommended version to rebuild the projects is V6.30. But the examples are all prebuild and work out-of-the box with Ozone, so rebuilding is not necessary.

Streaming trace

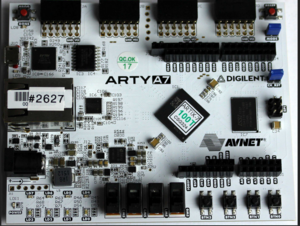

The project below has been tested with the minimum requirements mentioned above and a Digilent AVNET ARTY A7 100T board. The board is loaded with an FPGA bitstream for the SiFive E31 core. The bitstream must support SiFive Nexus BTM with trace pins as a trace sink option.

FPGA bitstreams can be requested at the SiFive website.

For connection of the board to the J-Trace Pro RISC-V the SiFive ARTY Trace Adapter may be used.

Example project: SiFive_E31_TracePins.zip

Trace buffer

For buffer tracing the same project above can be used. Simply change the trace settings in Ozone to trace buffer via Tools->Trace Settings...->Trace Source-> Trace Buffer