SiFive Nexus Trace technical specification

When using the J-Trace PRO as a debugging tool it is crucial for a successful session that the trace data output by the microcontroller is following the correct protocol standard. The trace clock speed (TRACECLK) is on most microcontrollers directly dependent on the CPU clock speed and usually half the CPU clock speed. In the SiFive Nexus Trace implementation two different protocol modes can be active. The following article will display the two modes and which components need to be implemented in your target device so instruction tracing is available.

Contents

SiFive Nexus Trace parallel protocol

The SiFive Nexus Trace parallel protocol has two operating modes which is toggled via the configuration bit pibRefCenter. Per default pibRefCenter will be configured to 0 in our software. This can be changed via exec command if needed.

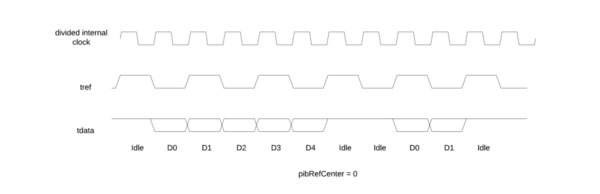

pibRefCenter = 0

In this mode the TRACECLK is exactly 1/2 of the CPU clock speed and sampling is done with both flanks. Data and TRACELCK are output at the same time. While this can cause issues with sampling it is no problem for the J-Trace Pro as there is a build in delay between in our hardware which is also configurable.

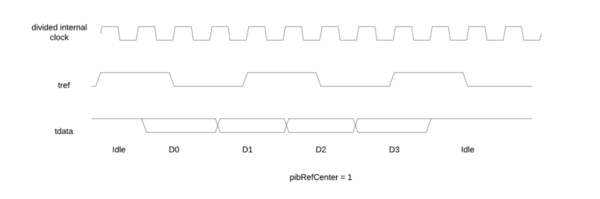

pibRefCenter = 1

In this mode the TRACECLK is exactly 1/4 of the CPU clock speed and sampling is done with both flanks. Data and TRACELCK are output with a 90° phase shift. This reduces the risk of sampling incorrect that as the trace data had more time to settle before it is sampled with the next TRACECLK impulse.

Solution for out of spec signals

If the target device should not be outputting signals that fulfill the aforementioned requirements J-Trace PRO has a so called Trace timing configuration feature which compensates wrongly output trace data signals.

Required trace components

Minimum for buffer trace

- Trace Encoder

- SRAM Trace Sink

Minimum for pin tracing

- Trace pins + trace connector

- Trace Encoder

- PIB as Trace Sink

Optional for both setups

Available trace encoders

Branch Trace Mode (BTM)

BTM is comparable to Arm's PTM trace. So you get only basic trace where you only get trace data if the program flow changes through e.g. indirect branches or exceptions. Conditional instruction information is not available.

History Trace Mode (HTM)

HTM is comparable to Arm's ETMv4 trace. It has additional trace packet compression and conditional instruction information is processed.