Difference between revisions of "SiFive S54 Standard Core Dev Kit"

(→Programming the bitstream) |

(→Programming the bitstream) |

||

| Line 26: | Line 26: | ||

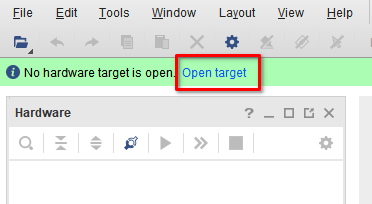

* '''Select FPGA -> Right-click -> Add Configuration Memory Device''' |

* '''Select FPGA -> Right-click -> Add Configuration Memory Device''' |

||

*;[[File: ARTY-100T_VivadoLAB_AddConfigMem.png | none]] |

*;[[File: ARTY-100T_VivadoLAB_AddConfigMem.png | none]] |

||

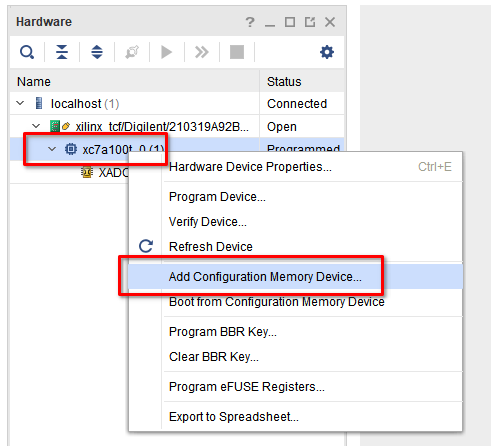

| + | * Select the appropriate flash device as shown in the screenshot below |

||

| + | *;[[File: ARTY-100T_VivadoLAB_SelFlash.png | none]] |

||

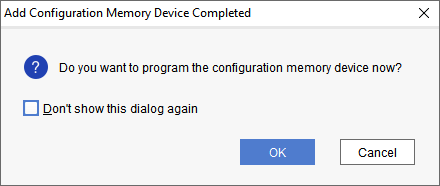

* Confirm the following dialog with '''OK''' |

* Confirm the following dialog with '''OK''' |

||

*;[[File: ARTY-100T_VivadoLAB_ConfirmProgram.png | none]] |

*;[[File: ARTY-100T_VivadoLAB_ConfirmProgram.png | none]] |

||

Revision as of 12:29, 21 May 2021

Contents

This article describes specifics for the SiFive S54 Standard Core Dev Kit. The SiFive S54 Standard Core Dev Kit implements a SiFive S54 (64-bit RV64) core as a FPGA bitstream that runs on the Digilent ARTY-100T eval board.

Getting the bitstream running

Prerequisites

To program the bitstream:

- SiFive S54 Standard Core Dev Kit: sifive.com

- Digilent ARTY-100T FPGA eval board (~200 EUR)

- Xilinx Vivado LAB (free)

- Micro USB cable

After the bitstream has been programmed:

- J-Link BASE or higher: Model overview

- SEGGER SiFive-ARTY adapter

Programming the bitstream

In this article, Vivado LAB 2017.2 was used but the steps should be identical / very similar for later versions.

- Supply power to the ARTY-100T board via the power jack (7V, center positive)

- Connect the ARTY-100T board via micro USB cable to the computer

- Start Vivado LAB

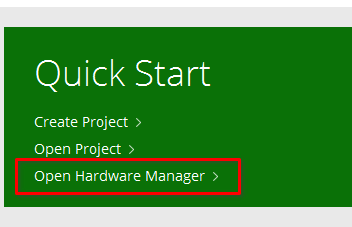

- Click Open Hardware Manager

- Click Open Target -> Auto Connect

- Select FPGA -> Right-click -> Add Configuration Memory Device

- Select the appropriate flash device as shown in the screenshot below

- Confirm the following dialog with OK

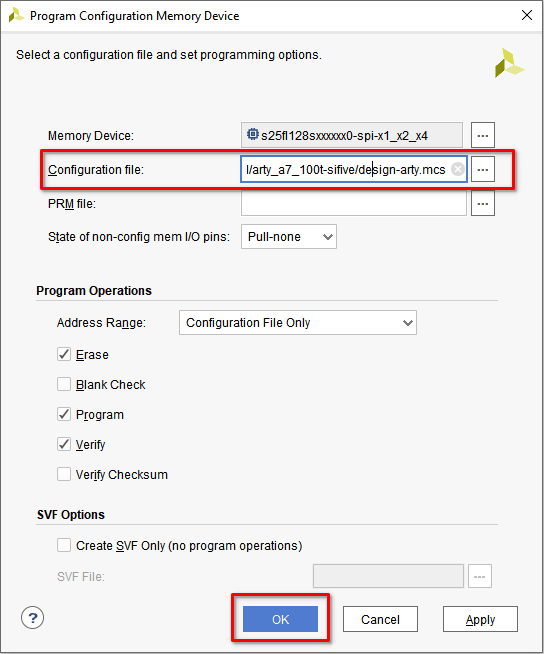

- Select the MCS file (bitstream) for the S54 from the SiFive dev kit package and set the programming settings

as shown in the screenshot below and confirm with OK afterwards

The MCS file for the S54 is located under: sifive_s54_rtl_eval_llama.02.00rc1-general\arty_a7_100t-sifive\design-arty.mcs - Wait for about 30 seconds for programming to complete

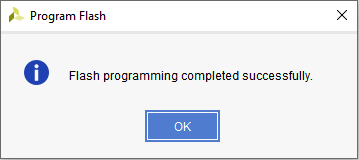

- Once programming has finished, confirm the dialog with OK

- Close Vivado LAB

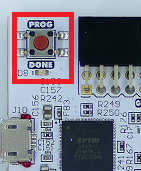

- Push the PROG button on the ARTY-100T board to load the bitstream into the FPGA

(Only needed once after programming. Bitstream is auto-loaded on power cycle of board, from now on) - Wait until the DONE LED lights up again.

Verifying the debug connection

- Connect the SEGGER SiFive-ARTY adapter to connector JD on the ARTY-100T board

- Connect J-Link to the SEGGER SiFive-ARTY adapter

- Start J-Link Commander with device selection S54 and TIF == JTAG and verify the connection.

- <Picture>