Difference between revisions of "Tracing on Renesas R7S721001WS (RZ/A1H)"

(→Minimum requirements) |

|||

| Line 5: | Line 5: | ||

ETB tracing is implemented as well and can be used even with a J-Link. |

ETB tracing is implemented as well and can be used even with a J-Link. |

||

| − | = Minimum requirements = |

+ | == Minimum requirements == |

In order to use pin trace on the Renesas R7S721001WS (RZ/A1H) devices, the following minimum requirements have to be met: |

In order to use pin trace on the Renesas R7S721001WS (RZ/A1H) devices, the following minimum requirements have to be met: |

||

* J-Link software version V6.32g or later |

* J-Link software version V6.32g or later |

||

| Line 11: | Line 11: | ||

* J-Trace PRO for Cortex HW version V2.0 or later |

* J-Trace PRO for Cortex HW version V2.0 or later |

||

| − | = Sample project = |

+ | == Sample project == |

| − | == Streaming trace == |

+ | === Streaming trace === |

The following sample project is designed to be used with J-Trace PRO and Ozone to demonstrate streaming trace. The project has been tested with the minimum requirements mentioned above and a ''RSK2+RZA1H board''. The sample project comes with a pre-configured project file for Ozone that runs out-of-the box. In order to rebuild the sample project, [https://www.segger.com/embedded-studio.html SEGGER Embedded Studio] can be used. |

The following sample project is designed to be used with J-Trace PRO and Ozone to demonstrate streaming trace. The project has been tested with the minimum requirements mentioned above and a ''RSK2+RZA1H board''. The sample project comes with a pre-configured project file for Ozone that runs out-of-the box. In order to rebuild the sample project, [https://www.segger.com/embedded-studio.html SEGGER Embedded Studio] can be used. |

||

[[Media:Renesas_RZ_A1H_33MHz_TraceEx_pex.zip | Renesas_RZ_A1H_33MHz_TraceExample.zip]] |

[[Media:Renesas_RZ_A1H_33MHz_TraceEx_pex.zip | Renesas_RZ_A1H_33MHz_TraceExample.zip]] |

||

| − | = Tested Hardware = |

+ | == Tested Hardware == |

[[File:RZ_A1H.jpg|none|thumb|RSK2+RZA1H board]] |

[[File:RZ_A1H.jpg|none|thumb|RSK2+RZA1H board]] |

||

| − | = Reference trace signal quality = |

+ | == Reference trace signal quality == |

The following pictures show oscilloscope measurements of trace signals output by the "Tested Hardware" using the example project. |

The following pictures show oscilloscope measurements of trace signals output by the "Tested Hardware" using the example project. |

||

All measurements have been performed using a Agilent InfiniiVision DSO7034B 350 MHz 2GSa/s oscilloscope and 1156A 1.5 GHz Active Probes. If your trace signals look similar on your trace hardware, chances are good that tracing will work out-of-the-box using the example project. |

All measurements have been performed using a Agilent InfiniiVision DSO7034B 350 MHz 2GSa/s oscilloscope and 1156A 1.5 GHz Active Probes. If your trace signals look similar on your trace hardware, chances are good that tracing will work out-of-the-box using the example project. |

||

More information about correct trace timing can be found at the following [https://www.segger.com/products/debug-probes/j-trace/technology/setting-up-trace/ website]. |

More information about correct trace timing can be found at the following [https://www.segger.com/products/debug-probes/j-trace/technology/setting-up-trace/ website]. |

||

| − | == Rise time == |

+ | === Rise time === |

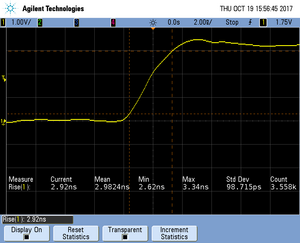

The rise time of a signal shows the time needed for a signal to rise from logical 0 to logical 1. For this the values at 10% and 90% of the expected voltage level get used as markers. The following picture shows such a measurement for the trace clock signal. |

The rise time of a signal shows the time needed for a signal to rise from logical 0 to logical 1. For this the values at 10% and 90% of the expected voltage level get used as markers. The following picture shows such a measurement for the trace clock signal. |

||

[[File:A1H_Ristetime_TCLK.png|none|thumb|TCLK rise time]] |

[[File:A1H_Ristetime_TCLK.png|none|thumb|TCLK rise time]] |

||

| − | == Setup time == |

+ | === Setup time === |

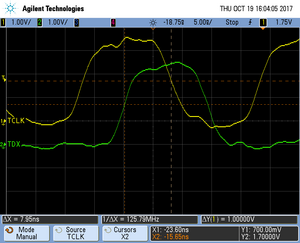

The setup time shows the relative setup time between a trace data signal and trace clock. The measurement markers are set at 50% of the expected voltage level respectively. The following picture shows such a measurement for the trace data signal 0 relative to the trace clock signal. |

The setup time shows the relative setup time between a trace data signal and trace clock. The measurement markers are set at 50% of the expected voltage level respectively. The following picture shows such a measurement for the trace data signal 0 relative to the trace clock signal. |

||

[[File:A1H__Setuptime_TD0.png|none|thumb|TD0 setup time]] |

[[File:A1H__Setuptime_TD0.png|none|thumb|TD0 setup time]] |

||

Revision as of 18:08, 13 November 2020

Contents

This article describes how to get started with trace on the Renesas R7S721001WS (RZ/A1H) MCU. This article assumes that there is already a basic knowledge about trace in general (what is trace, what different implementations of trace are there, etc.). If this is not the case, we recommend to read Trace chapter in the J-Link User Manual (UM08001). The Renesas R7S721001WS (RZ/A1H) MCU implements tracing via pins , so a J-Trace can be used for tracing. ETB tracing is implemented as well and can be used even with a J-Link.

Minimum requirements

In order to use pin trace on the Renesas R7S721001WS (RZ/A1H) devices, the following minimum requirements have to be met:

- J-Link software version V6.32g or later

- Ozone V2.56r or later (if streaming trace and / or the sample project from below shall be used)

- J-Trace PRO for Cortex HW version V2.0 or later

Sample project

Streaming trace

The following sample project is designed to be used with J-Trace PRO and Ozone to demonstrate streaming trace. The project has been tested with the minimum requirements mentioned above and a RSK2+RZA1H board. The sample project comes with a pre-configured project file for Ozone that runs out-of-the box. In order to rebuild the sample project, SEGGER Embedded Studio can be used.

Renesas_RZ_A1H_33MHz_TraceExample.zip

Tested Hardware

Reference trace signal quality

The following pictures show oscilloscope measurements of trace signals output by the "Tested Hardware" using the example project. All measurements have been performed using a Agilent InfiniiVision DSO7034B 350 MHz 2GSa/s oscilloscope and 1156A 1.5 GHz Active Probes. If your trace signals look similar on your trace hardware, chances are good that tracing will work out-of-the-box using the example project. More information about correct trace timing can be found at the following website.

Rise time

The rise time of a signal shows the time needed for a signal to rise from logical 0 to logical 1. For this the values at 10% and 90% of the expected voltage level get used as markers. The following picture shows such a measurement for the trace clock signal.

Setup time

The setup time shows the relative setup time between a trace data signal and trace clock. The measurement markers are set at 50% of the expected voltage level respectively. The following picture shows such a measurement for the trace data signal 0 relative to the trace clock signal.