Difference between revisions of "PSoC 4xxx series"

(→Connection behavior) |

(→Connection behavior) |

||

| Line 5: | Line 5: | ||

A locked PSoC 4 device is automatically set to ''open'' if it was in ''protected'' state. |

A locked PSoC 4 device is automatically set to ''open'' if it was in ''protected'' state. |

||

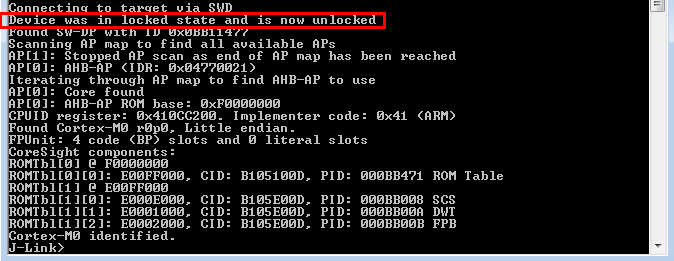

If the device was unlocked, following message is shown: |

If the device was unlocked, following message is shown: |

||

| − | |||

| − | ''Device was in locked state and is now unlocked'' |

||

[[File:Device_was_unlocked.PNG]] |

[[File:Device_was_unlocked.PNG]] |

||

Revision as of 14:15, 16 July 2019

This page contains information about the Cypress PSoC 4xxx series.

Contents

Connection behavior

The connect sequence of PSoC 4 devices is very time critical and is performed from the J-Link's side directly. A locked PSoC 4 device is automatically set to open if it was in protected state. If the device was unlocked, following message is shown:

Readout protection

Securing device after programming

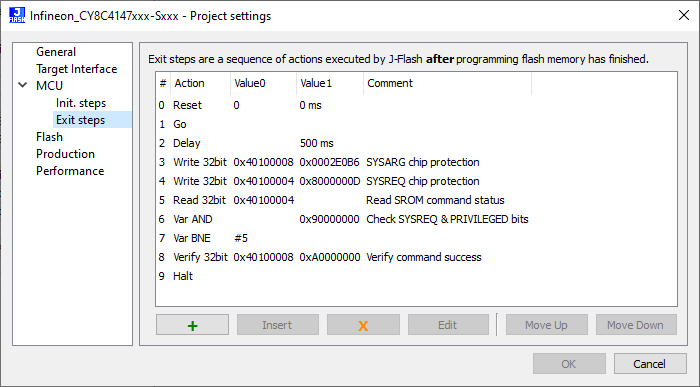

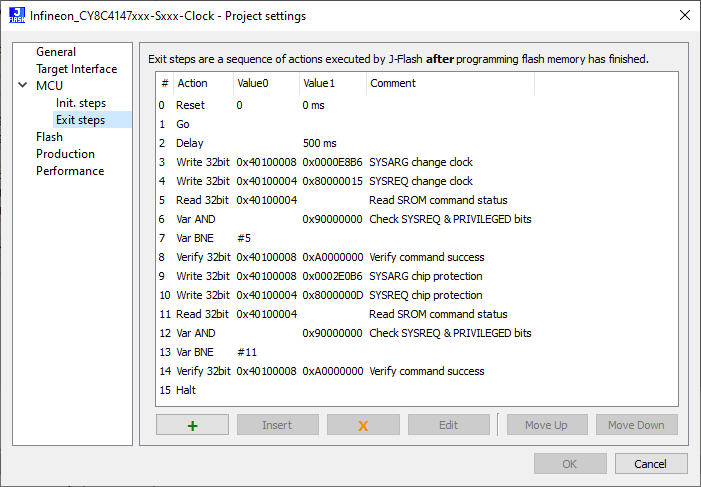

The Cypress CY8C4xxx and CYBLExxxx series devices provide chip-level protection which allows "permanent" protection of the device concerning read and write access. The sequence, to secure the device consists of multiple read / write accesses to special function registers of the CY8C4xxx and CYBLExxxx series devices.

Via J-Flash / Flasher ARM

The sequence to secure the device, needs to be added to the exit-steps of the J-Flash project. The exit steps will be executed at the end of an successful auto-programming process (Target -> Auto). J-Flash comes with an example project for the Cypress CYBLE-214009-00 device which contains a secure device programming sequence (File:Cypress CYBLE 214009-00.jflash). This sequence applies for all Cypress CY8C4xxx and CYBLExxxx series devices since they are compatible regarding secure procedure and can be adapted to fit custom requirements, by re-selecting the required device within the J-Flash project.

Note: PSoC4100/4200 target devices use different addresses for the SYSREQ and SYSARG registers. They are located at 0x40000004 and 0x40000008 instead. For more information please consult the CypressProgramming Specifications user guide.

Note2: The clock of PSoC41x7-BL and PSoC42x7-BL target devices must be set to 48MHz before calling the locking/unlocking sequence. This can be acquired by using the "Configure Clock" Command.

Unsecuring device before reprogramming

The Cypress CY8C4xxx and CYBLExxxx series devices provide chip-level protection which allows "permanent" protection of the device concerning read and write access. The sequence, to unsecure the device consists of multiple read / write accesses to special function registers of the Cypress CY8C4xxx and CYBLExxxx series devices MCU.

Via J-Flash / Flasher ARM

J-Flash(v6.31k and following) detects if the device is secured. In case of a secured device it will unsecure it. This sequence applies for all Cypress CY8C4xxx and CYBLExxxx series devices since they are compatible regarding secure procedure.