Difference between revisions of "ArteryTek AT-START-F415"

(Created page with "__TOC__ This article describes specifics for the Artery AT-START-F415 evaluation board.<br> 450px == Preparing for J-Li...") |

(→Preparing for J-Link) |

||

| Line 12: | Line 12: | ||

|- |

|- |

||

| GND || J1 || 31 || GND |

| GND || J1 || 31 || GND |

||

| + | |- |

||

| + | | TDI || J1 || 14 || PA15 |

||

|- |

|- |

||

| TMS/SWDIO || J1 || 14 || PA13/SWDIO |

| TMS/SWDIO || J1 || 14 || PA13/SWDIO |

||

| Line 21: | Line 23: | ||

| RESET || J2 || 7 || NRST |

| RESET || J2 || 7 || NRST |

||

|} |

|} |

||

| − | *Power the board via USB |

+ | *Power the board via USB CN6. |

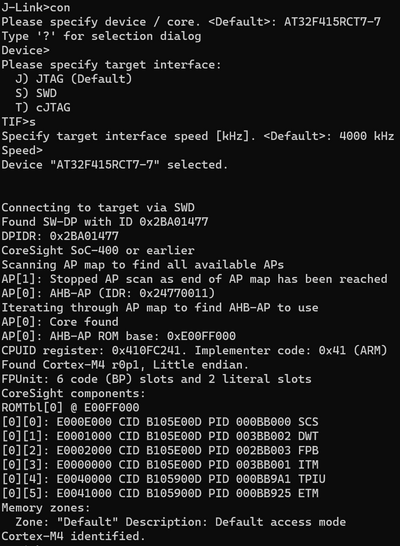

* Verify the Connection with e.g. [https://wiki.segger.com/J-Link_cannot_connect_to_the_CPU#Verify_functionality_using_J-Link_Commander J-Link Commander]. The output should look as follows: |

* Verify the Connection with e.g. [https://wiki.segger.com/J-Link_cannot_connect_to_the_CPU#Verify_functionality_using_J-Link_Commander J-Link Commander]. The output should look as follows: |

||

[[File:Artery_AT-START-F415_AT32F415RCT7-7_connect.png|400px]] |

[[File:Artery_AT-START-F415_AT32F415RCT7-7_connect.png|400px]] |

||

Revision as of 15:45, 23 January 2024

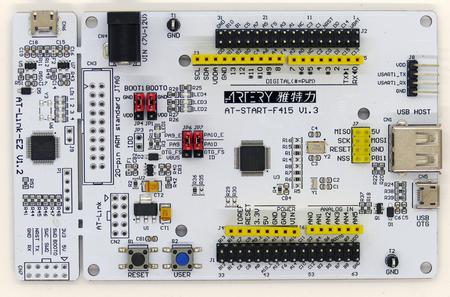

This article describes specifics for the Artery AT-START-F415 evaluation board.

Preparing for J-Link

- Connect the J-Link to this pins:

| J-Link Pin | Connector | Pin | Name |

|---|---|---|---|

| VTref | J1 | 32 | VDD |

| GND | J1 | 31 | GND |

| TDI | J1 | 14 | PA15 |

| TMS/SWDIO | J1 | 14 | PA13/SWDIO |

| TCK/SWCLK | J1 | 17 | PA14/SWCLK |

| TDO/SWO | J1 | 23 | PB3 |

| RESET | J2 | 7 | NRST |

- Power the board via USB CN6.

- Verify the Connection with e.g. J-Link Commander. The output should look as follows:

Example Project

The following example project was created with the SEGGER Embedded Studio project wizard and runs out-of-the-box on the Artery AT-START-F415.

It is a simple Hello World sample linked into the internal flash.

SETUP

- J-Link software: V7.94g

- Embedded Studio: V7.20

- Hardware: Artery AT-START-F415

- Link: File:Artery AT-START-F415 AT32F415RCT7-7 TestProject ES 7V20.zip