ArteryTek AT-START-F423

Revision as of 10:31, 23 January 2024 by Torben.scharping (talk | contribs) (Created page with "__TOC__ This article describes specifics for the Artery AT-START-F423 evaluation board.<br> 450px == Preparing for J-Link...")

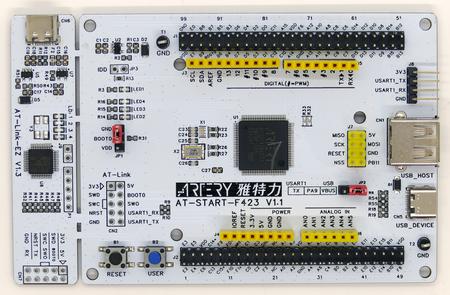

This article describes specifics for the Artery AT-START-F423 evaluation board.

Preparing for J-Link

- Connect the J-Link to this pins:

| J-Link Pin | Connector | Pin | Name |

|---|---|---|---|

| VTref | J1 | 24 | VDD |

| GND | J1 | 23 | GND |

| SWDIO | J1 | 10 | PA13 |

| SWCLK | J1 | 13 | PA14 |

| RESET | J2 | 7 | NRST |

- Power the board via CH4.

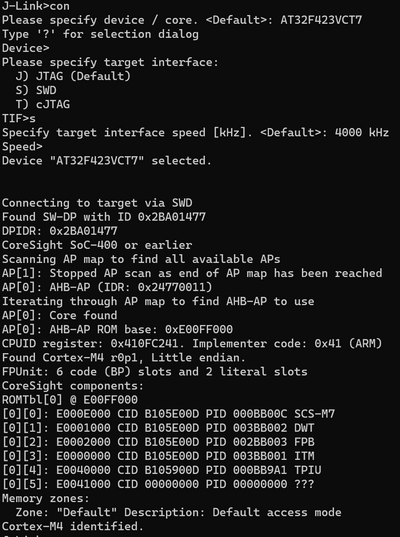

- Verify the Connection with e.g. J-Link Commander. The output should look as follows:

Example Project

The following example project was created with the SEGGER Embedded Studio project wizard and runs out-of-the-box on the Artery AT-START-F423.

It is a simple Hello World sample linked into the internal flash.

SETUP

- J-Link software: V7.94g

- Embedded Studio: V7.20

- Hardware: Artery AT-START-F422

- Link: File:Artery AT-START-F423 AT32F423VCT7 TestProject ES 7V20.zip