Difference between revisions of "Infineon CY-SD2220"

| Line 3: | Line 3: | ||

This article describes specifics for the Infineon CY-SD2220 evaluation board.<br> |

This article describes specifics for the Infineon CY-SD2220 evaluation board.<br> |

||

'''[PICTURE OF BOARD]''' |

'''[PICTURE OF BOARD]''' |

||

| − | [[File: |

+ | [[File:Infineon_CY-SD2220_Rev01_CYPD7191-40LDXS_board.jpg|450px]] |

== Preparing for J-Link == |

== Preparing for J-Link == |

||

Revision as of 12:51, 27 December 2023

This article describes specifics for the Infineon CY-SD2220 evaluation board.

[PICTURE OF BOARD]

Preparing for J-Link

- Connect the J-Link to J18:

- GND on J18.2

- SWDIO on J18.5

- SWCLK on J18.4

- Reset on J18.3

- VTref on TP13

- Power the board via J5.

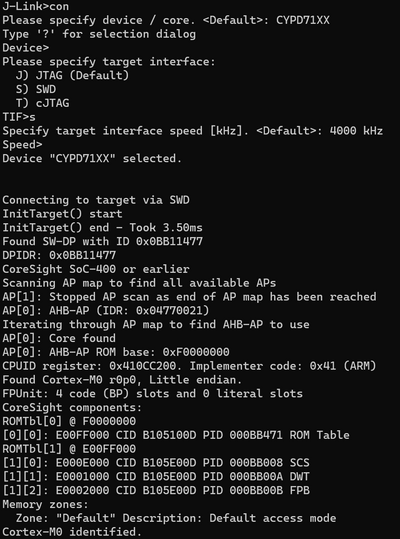

- Verify the Connection with e.g. J-Link Commander. The output should look as follows:

Example Project

The following example project was created with the SEGGER Embedded Studio project wizard and runs out-of-the-box on the Infineon CY-SD2220.

It is a simple Hello World sample linked into the internal flash.

SETUP

- J-Link software: V7.xx

- Embedded Studio: V7.20

- Hardware: [SiliconVendor] [EvalBoardName]

- Link: File:VENDOR DEVICENAME TestProject ES V452b.zip