Difference between revisions of "Tracing on Infineon XMC4500 series MCUs"

(Created page with "__TOC__ This article describes how to add support for new devices / flash banks to the J-Link DLL so that they can be used with any J-Link DLL based application like for examp...") |

|||

| (35 intermediate revisions by 5 users not shown) | |||

| Line 1: | Line 1: | ||

__TOC__ |

__TOC__ |

||

| − | This article describes how to add support for new devices / flash banks to the J-Link DLL so that they can be used with any J-Link DLL based application like for example J-Flash, J-Link Commander, IDEs, etc...This article assumes that there is already a basic understanding of the method of adding new devices using the Open Flashloader concept. If this is not the case, we recommend to read the '''Open Flashloader''' chapter in the J-Link User Manual (UM08001). In general, there are two possibilities to add support for a new device: |

||

| − | #'''Use a pre-compiled flash loader''' |

||

| − | #'''Compile / create the flash loader on your own''' |

||

| − | ##Using Keil uVision (a license is required, no trial available; Supports Cortex-M, only) |

||

| − | ##SEGGER Embedded Studio (can be evaluated without license; Supports Cortex-M and Cortex-A/R)<br>How to create a flash loader on your own using Embedded Studio is described below. |

||

| − | = Creating a flash algorithm using SEGGER Embedded Studio = |

||

| − | This article describes how to create a flash loader using the template projects (Cortex-M and Cortex-A/R) for SEGGER Embedded Studio. |

||

| − | == Debug Configurations == |

||

| − | The example project contains two debug configurations: |

||

| − | *Debug |

||

| − | *Release |

||

| − | === Debug configuration === |

||

| − | This configuration allows to debug the flash algorithm in Embedded Studio. The configuration includes a main.c containing the typical function call order, executed by the J-Link DLL during flash programming. The optimization level for this configuration is set to "none". |

||

| − | === Release configuration === |

||

| − | This configuration does not allow debugging but creates the output elf file which can be referenced from within the JLinkDevices.xml file as "''Loader''". The optimization level is set to 3 (highest). |

||

| − | == Included files == |

||

| − | {| class="wikitable" |

||

| − | |- |

||

| − | ! Filename !! Content |

||

| − | |- |

||

| − | | '''FlashDev.c''' || Flash device description for the ST STM32F205RC |

||

| − | |- |

||

| − | | '''FlashOS.h''' || Function prototypes, definitions and structures |

||

| − | |- |

||

| − | | '''FlashPrg.c''' || Flash algorithm itself (e.g. ProgramPage(), EraseSector() |

||

| − | |- |

||

| − | | '''main.c''' || Flash algorithm debug code (used by debug configuration, only) |

||

| − | |- |

||

| − | | '''Cortex_M_Startup.s'''<br>'''ARM_Startup.s''' || Cortex-M startup code (used by debug configuration, only) <br> Cortex-A/R startup code (used by debug configuration, only) |

||

| − | |- |

||

| − | | '''MemoryMap.xml''' || Memory map of the ST STM32F205RC |

||

| − | |- |

||

| − | | '''Placement_debug.xml''' || Debug configuration section placement file. |

||

| − | |- |

||

| − | | '''Placement_release.xml''' || Release configuration section placement file. |

||

| − | |- |

||

| − | | '''thumb_crt0.s'''<br>'''crt0.s''' || Initialization file for Cortex-M (used by debug configuration, only)<br>Initialization file for Cortex-A/R(used by debug configuration, only) |

||

| − | |} |

||

| − | == Embedded Studio Template Projects == |

||

| − | The template projects below have been tested with SEGGER Embedded Studio V3.10. |

||

| − | *[[File:OpenFlashLoader_CortexM_Template_EmbeddedStudio.zip]] |

||

| − | *[[File:OpenFlashLoader_CortexAR_Template_EmbeddedStudio.zip]] |

||

| + | This article describes how to get started with trace on the Infineon XMC4500 series. This article assumes that there is already a basic knowledge about trace in general (what is trace, what different implementations of trace are there, etc.). If this is not the case, we recommend to read '''Trace''' chapter in the J-Link User Manual (UM08001). |

||

| − | == Step-By-Step Instruction == |

||

| + | The Infineon XMC4500 series implements tracing via pins only, so a J-Trace is needed to perform tracing on these devices. |

||

| − | This step-by-step instruction explains how to create your own flash loader using the template projects for Embedded Studio and how to use add a new flash bank for an existing or new device to the J-Link DLL, so that it can be used from within any application using the DLL. |

||

| − | #Adapt the template project |

||

| − | ##'''FlashDev.c''': Modify the FlashDevice structure according to your device |

||

| − | ##'''FlashPrg.c''': Implement the flash routines Init(), UnInit(), EraseSector() and ProgramPage() |

||

| − | ##'''MemoryMap.xml''': Enter RAM base address and RAM size |

||

| − | ##'''main.c''': Make sure that the define ''_FLASH_BASE_ADDR'' defines the correct flash base address |

||

| − | #Test the debug configuration |

||

| − | ##Connect the target to the J-Link and the J-Link to the PC |

||

| − | ##Switch to the '''Debug''' configuration in Embedded Studio ('''Build''' -> '''Set Active Build Configuration''' -> '''Debug''') |

||

| − | ##Build the project by pressing '''F7''' |

||

| − | ##Start the debug session by pressing '''F5''' |

||

| − | ##PC should be halted at main. Now debug the flash algorithm and make sure that it behaves as expected. |

||

| − | #Build the flash loader using the release configuration |

||

| − | ##Switch to the '''Release''' configuration in Embedded Studio ('''Build''' -> '''Set Active Build Configuration''' -> '''Release''') |

||

| − | ##Build the project by pressing '''F7''' --> The flash loader file can be found here: $PROJ_DIR$\Output\Release\Exe\*.elf |

||

| − | #JLinkDevices.xml |

||

| − | ##Create or adapt the '''JLinkDevices.xml''' (described in the J-Link User Manual (UM08001)). |

||

| − | ##Place the '''JLinkDevices.xml''' file at the correct location (described in the J-Link User Manual (UM08001)). |

||

| − | Now you can select and use the created or adapted device which uses the new flash bank in any J-Link DLL based application (e.g. J-Link Commander / IDE / ...). |

||

| − | == Frequently Asked Questions == |

||

| − | In which order does the J-Link DLL call the function during flash programming? |

||

| − | #Compare |

||

| − | ##Init() |

||

| − | ##Compare()<br>Memory is accessed so it has to be initialized during Init() so that it can be memory mapped accessed here. If it is not initialized correctly, the read access may results in confusing the MCU. |

||

| − | ##UnInit() |

||

| − | # Erase |

||

| − | ## Init() |

||

| − | ## Erase() |

||

| − | ## UnInit() |

||

| − | # Program |

||

| − | ## Init() |

||

| − | ## Program() |

||

| − | ## UnInit() |

||

| − | == Troubleshoot == |

||

| − | This section provides assistance in case of issues pops up when using custom added flash bank. The section assumes that the functionality has been verified using the debug configuration in Embedded Studio. |

||

| − | #Get the latest version of the template project |

||

| − | #Follow the Step-By-Step instructions expect of 2.1 FlashPrg.c --> Functions should not contain any code that accesses any SFRs |

||

| − | #Build the flash loader using the release configuration |

||

| − | #Perform a flash download using J-Link Commander. Flash download should report an error during verify |

||

| − | #Implement EraseSector() and retry the flash download test. J-Link Commander should still report verify failed but effected flash memory region should be empty. If not, check EraseSector(). |

||

| − | #Implement ProgramPage() and retry the flash download test. Expected result: Test reports O.K. --> Programmed successfully. If not, check ProgramPage() code. |

||

| − | == |

+ | == Minimum requirements == |

| + | In order to use trace on the Infineon XMC4500 series devices, the following minimum requirements have to be met: |

||

| − | === PC has unexpected value after flash download === |

||

| + | * J-Link software version V6.18c or later |

||

| − | This error may have different root causes: |

||

| + | * Ozone V2.46a or later (if streaming trace and / or the sample project from below shall be used) |

||

| − | *Watchdog is enabled but not fed in the flash loader functions. This may result in a watchdog timeout pops up during RAMCode execution. The behavior is different but usually a reset will be triggered. |

||

| + | * J-Trace PRO for Cortex-M HW version V1.0 or later |

||

| − | *Accessing not enabled / clocked special function registers / peripherals |

||

| + | To rebuild the project our IDE Embedded Studio can be used. The recommended version to rebuild the projects is V6.30. But the examples are all prebuild and work out-of-the box with Ozone, so rebuilding is not necessary. |

||

| − | *Accessing invalid memory regions (reserved) |

||

| + | |||

| − | ===(Q)SPI flashes=== |

||

| + | == Sample project == |

||

| − | *The Init() code has to make sure that the (Q)SPI pins as well as the (Q)SPI controller are configured so that the flash can be memory mapped (read) accessed. This is necessary as the J-Link DLL reads the data before programming to check if flash content does already match. This can be validated by setting the compare method in J-Link Commander to "skip" (exec SetCompareMode 0). Now start flash download. J-Link Commander should report a verify error but the flash should be memmory mapped accessible from now. If not, check the Init() code. |

||

| + | The following sample project is designed to be used with J-Trace PRO and Ozone to demonstrate streaming trace. The project has been tested with the minimum requirements mentioned above on a XMC4500_CPU_45A-V3 Kit (Hexagon Board). The sample project comes with a pre-configured project file for Ozone that runs out-of-the box. In order to rebuild the sample project, [https://www.segger.com/embedded-studio.html SEGGER Embedded Studio] can be used. But the examples are all pre-build and work out-of-the box with Ozone, so rebuilding is not necessary. |

||

| + | |||

| + | [[Media:Infineon XMC4500-1024 CPU 45A-V3 120MHz TraceExample pex.zip | Infineon XMC4500-1024 CPU 45A-V3 120MHz TraceExample.zip]] |

||

| + | |||

| + | {{Note|The example is shipped with a compiled .JLinkScriptfile, should you need the original source, please get in touch with SEGGER directly via our support system: https://www.segger.com/ticket/.<br> |

||

| + | |||

| + | To create your own .JLinkScriptfile you can use the following guide as reference: [[How_to_configure_JLinkScript_files_to_enable_tracing]] |

||

| + | |||

| + | }} |

||

| + | |||

| + | == Tested Hardware == |

||

| + | [[File:Infineon_XMC4500_CPU_45A-V3_Kit.jpg|none|thumb|XMC4500_CPU_45A-V3 Kit (Hexagon Board)]] |

||

| + | |||

| + | == Reference trace signal quality == |

||

| + | The following pictures show oscilloscope measurements of trace signals output by the "Tested Hardware" using the example project. |

||

| + | All measurements have been performed using a Agilent InfiniiVision DSO7034B 350 MHz 2GSa/s oscilloscope and 1156A 1.5 GHz Active Probes. If your trace signals look similar on your trace hardware, chances are good that tracing will work out-of-the-box using the example project. |

||

| + | More information about correct trace timing can be found at the following [https://www.segger.com/products/debug-probes/j-trace/technology/setting-up-trace/ website]. |

||

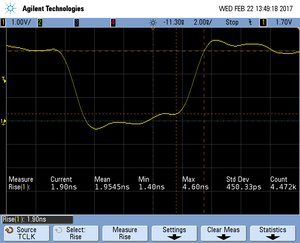

| + | === Rise time === |

||

| + | The rise time of a signal shows the time needed for a signal to rise from logical 0 to logical 1. For this the values at 10% and 90% of the expected voltage level get used as markers. The following picture shows such a measurement for the trace clock signal. |

||

| + | [[File:XMC4500_TCLK_Risetime.png|none|thumb|TCLK rise time]] |

||

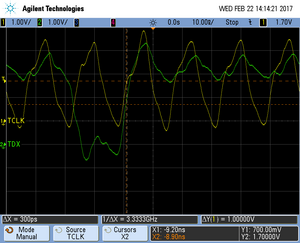

| + | === Setup time === |

||

| + | The setup time shows the relative setup time between a trace data signal and trace clock. The measurement markers are set at 50% of the expected voltage level respectively. The following picture shows such a measurement for the trace data signal 0 relative to the trace clock signal. |

||

| + | [[File:XMC4500_TD0_Setuptime.png|none|thumb|TD0 setup time]] |

||

Latest revision as of 14:32, 15 August 2023

Contents

This article describes how to get started with trace on the Infineon XMC4500 series. This article assumes that there is already a basic knowledge about trace in general (what is trace, what different implementations of trace are there, etc.). If this is not the case, we recommend to read Trace chapter in the J-Link User Manual (UM08001). The Infineon XMC4500 series implements tracing via pins only, so a J-Trace is needed to perform tracing on these devices.

Minimum requirements

In order to use trace on the Infineon XMC4500 series devices, the following minimum requirements have to be met:

- J-Link software version V6.18c or later

- Ozone V2.46a or later (if streaming trace and / or the sample project from below shall be used)

- J-Trace PRO for Cortex-M HW version V1.0 or later

To rebuild the project our IDE Embedded Studio can be used. The recommended version to rebuild the projects is V6.30. But the examples are all prebuild and work out-of-the box with Ozone, so rebuilding is not necessary.

Sample project

The following sample project is designed to be used with J-Trace PRO and Ozone to demonstrate streaming trace. The project has been tested with the minimum requirements mentioned above on a XMC4500_CPU_45A-V3 Kit (Hexagon Board). The sample project comes with a pre-configured project file for Ozone that runs out-of-the box. In order to rebuild the sample project, SEGGER Embedded Studio can be used. But the examples are all pre-build and work out-of-the box with Ozone, so rebuilding is not necessary.

Infineon XMC4500-1024 CPU 45A-V3 120MHz TraceExample.zip

The example is shipped with a compiled .JLinkScriptfile, should you need the original source, please get in touch with SEGGER directly via our support system: https://www.segger.com/ticket/.

To create your own .JLinkScriptfile you can use the following guide as reference: How_to_configure_JLinkScript_files_to_enable_tracing

Tested Hardware

Reference trace signal quality

The following pictures show oscilloscope measurements of trace signals output by the "Tested Hardware" using the example project. All measurements have been performed using a Agilent InfiniiVision DSO7034B 350 MHz 2GSa/s oscilloscope and 1156A 1.5 GHz Active Probes. If your trace signals look similar on your trace hardware, chances are good that tracing will work out-of-the-box using the example project. More information about correct trace timing can be found at the following website.

Rise time

The rise time of a signal shows the time needed for a signal to rise from logical 0 to logical 1. For this the values at 10% and 90% of the expected voltage level get used as markers. The following picture shows such a measurement for the trace clock signal.

Setup time

The setup time shows the relative setup time between a trace data signal and trace clock. The measurement markers are set at 50% of the expected voltage level respectively. The following picture shows such a measurement for the trace data signal 0 relative to the trace clock signal.