Difference between revisions of "Infineon EVAL PMG1 B1 DRP"

(Created page with "Category:Evalboards __TOC__ This article describes specifics for the [SiliconVendor] [EvalBoardName] evaluation board.<br> '''[PICTURE OF BOARD]''' File:VENDOR_BOARDNAM...") |

|||

| (2 intermediate revisions by the same user not shown) | |||

| Line 2: | Line 2: | ||

__TOC__ |

__TOC__ |

||

| − | This article describes specifics for the |

+ | This article describes specifics for the Infineon EVAL PMG1 B1 DRP evaluation board.<br> |

'''[PICTURE OF BOARD]''' |

'''[PICTURE OF BOARD]''' |

||

[[File:VENDOR_BOARDNAME.jpg|450px]] |

[[File:VENDOR_BOARDNAME.jpg|450px]] |

||

| − | |||

== Preparing for J-Link == |

== Preparing for J-Link == |

||

| + | |||

| − | *Connect the J-Link to ...... |

||

*Connect the J-Link to this pins: |

*Connect the J-Link to this pins: |

||

{| class="seggertable" |

{| class="seggertable" |

||

| Line 13: | Line 12: | ||

! J-Link Pin || Connector !! Pin || Name |

! J-Link Pin || Connector !! Pin || Name |

||

|- |

|- |

||

| − | | VTref || || || |

+ | | VTref || J4 || 1 || B1_VDDD |

|- |

|- |

||

| − | | GND || || || |

+ | | GND || J4 || 2 || GND |

|- |

|- |

||

| − | | |

+ | | TMS/SWDIO || J4 || 9 || SWDIO |

|- |

|- |

||

| − | | |

+ | | TCK/SWCLK || J4 || 7 || SWDCLK |

|- |

|- |

||

| − | | |

+ | | RESET || J4 || 5 || RESET |

| − | |- |

||

| − | | TCK/SWCLK || || || |

||

| − | |- |

||

| − | | RTCK || || || |

||

| − | |- |

||

| − | | TDO/SWO || || || |

||

| − | |- |

||

| − | | RESET || || || |

||

| − | |- |

||

| − | | DBGRQ || || || |

||

| − | |- |

||

| − | | 5V-Supply || || || |

||

| − | |||

|} |

|} |

||

| − | *Power the board via... |

+ | *Power the board via J1 9...22V. |

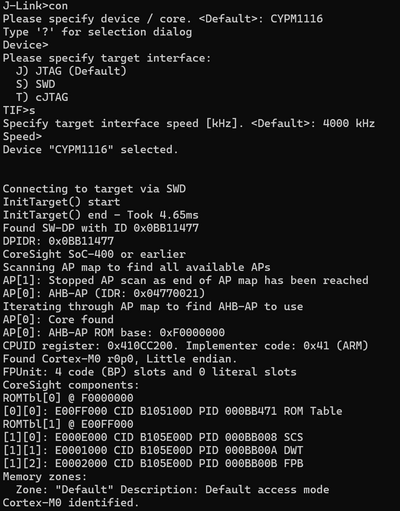

* Verify the Connection with e.g. [https://wiki.segger.com/J-Link_cannot_connect_to_the_CPU#Verify_functionality_using_J-Link_Commander J-Link Commander]. The output should look as follows: |

* Verify the Connection with e.g. [https://wiki.segger.com/J-Link_cannot_connect_to_the_CPU#Verify_functionality_using_J-Link_Commander J-Link Commander]. The output should look as follows: |

||

| + | [[File:Infineon_EVAL_PMG1_B1_DRP_CYPM1116-48LQXI_connect.png|400px]] |

||

| − | '''[PICTURE OF CONNECT]''' |

||

| − | [[File:VENDOR_DEVICE_CONNECT.PNG|400px]] |

||

== Example Project== |

== Example Project== |

||

| Line 45: | Line 30: | ||

====SETUP==== |

====SETUP==== |

||

*Embedded Studio: V7.20 |

*Embedded Studio: V7.20 |

||

| − | *Hardware: |

+ | *Hardware: Infineon EVAL PMG1 B1 DRP |

| − | *Link: [[File: |

+ | *Link: [[File:Infineon_CYPM1116_TestProject_ES_V720.zip]] |

| − | |||

| − | == Tracing on [DeviceName]== |

||

| − | This section describes how to get started with trace on the [SiliconVendor] [DeviceFamily] MCUs. |

||

| − | This section assumes that there is already a basic knowledge about trace in general (what is trace, what different implementations of trace are there, etc.). |

||

| − | If this is not the case, we recommend to read '''Trace''' chapter in the J-Link User Manual (UM08001). |

||

| − | {{Note|1= |

||

| − | * The sample projects come with a pre-configured project file for Ozone that runs out-of-the box. |

||

| − | * The following sample project is designed to be used with J-Trace PRO for streaming trace, J-Link Plus for buffer tracing (TMC/ETB trace) and Ozone to demonstrate streaming trace. |

||

| − | * In order to rebuild the sample project, [https://www.segger.com/embedded-studio.html SEGGER Embedded Studio] can be used. |

||

| − | * The examples are shipped with a compiled .JLinkScriptfile, should you need the original source, please get in touch with SEGGER directly via our support system: https://www.segger.com/ticket/. |

||

| − | ** To create your own .JLinkScriptfile you can use the following guide as reference: [[How_to_configure_JLinkScript_files_to_enable_tracing]] |

||

| − | }} |

||

| − | |||

| − | === Minimum requirements === |

||

| − | In order to use trace on the [SiliconVendor] [DeviceName] MCU devices, the following minimum requirements have to be met: |

||

| − | * J-Link software version Vx.xxx or later |

||

| − | * Ozone Vx.xxx or later (if streaming trace and / or the sample project from below shall be used) |

||

| − | * J-Trace PRO for Cortex-M HW version V3.0 or later for streaming trace |

||

| − | * J-Link Plus V12 or later for TMC/ETB trace |

||

| − | To rebuild the project our IDE Embedded Studio can be used. The recommended version to rebuild the projects is V6.30. But the examples are all prebuild and work out-of-the box with Ozone, so rebuilding is not necessary. |

||

| − | ==== Streaming trace ==== |

||

| − | The project below has been tested with the minimum requirements mentioned above and a ''[Boardname]''. |

||

| − | *'''Example project:''' [[Media:ExampleProject.zip | ExampleProject.zip]] |

||

| − | ==== Trace buffer (TMC/ETB) ==== |

||

| − | The project below is utilizing the on-chip trace buffer (it is '''not''' meant for streaming trace). |

||

| − | *'''Example Project:''' [[Media:ExampleProject.zip | ExampleProject.zip]] |

||

| − | ==== Tested Hardware ==== |

||

| − | [[File:Board.png|none|thumb|Board Name]] |

||

| − | ==== Specifics/Limitations(optional) ==== |

||

| − | The [BoardName] needs some modifications for all 4 trace data pins to work. For more information about this see the board specific user manual. |

||

| − | ==== Reference trace signal quality ==== |

||

| − | The following pictures show oscilloscope measurements of trace signals output by the "Tested Hardware" using the example project. |

||

| − | All measurements have been performed using a Agilent InfiniiVision DSO7034B 350 MHz 2GSa/s oscilloscope and 1156A 1.5 GHz Active Probes. |

||

| − | If your trace signals look similar on your trace hardware, chances are good that tracing will work out-of-the-box using the example project. |

||

| − | More information about correct trace timing can be found at the following [https://www.segger.com/products/debug-probes/j-trace/technology/setting-up-trace/ website]. |

||

| − | ===== Trace clock signal quality ===== |

||

| − | The trace clock signal quality shows multiple trace clock cycles on the tested hardware as reference. |

||

| − | [[File:TCLK.png|none|thumb|Trace clock signal quality]] |

||

| − | ===== Rise time ===== |

||

| − | The rise time of a signal shows the time needed for a signal to rise from logical 0 to logical 1. |

||

| − | For this the values at 10% and 90% of the expected voltage level get used as markers. The following picture shows such a measurement for the trace clock signal. |

||

| − | [[File:Risetime_TCLK.png|none|thumb|TCLK rise time]] |

||

| − | ===== Setup time ===== |

||

| − | The setup time shows the relative setup time between a trace data signal and trace clock. |

||

| − | The measurement markers are set at 50% of the expected voltage level respectively. |

||

| − | The following picture shows such a measurement for the trace data signal 0 relative to the trace clock signal. |

||

| − | [[File:Setuptime_TD0.png|none|thumb|TD0 setup time]] |

||

Latest revision as of 12:42, 13 May 2024

This article describes specifics for the Infineon EVAL PMG1 B1 DRP evaluation board.

[PICTURE OF BOARD]

450px

Preparing for J-Link

- Connect the J-Link to this pins:

| J-Link Pin | Connector | Pin | Name |

|---|---|---|---|

| VTref | J4 | 1 | B1_VDDD |

| GND | J4 | 2 | GND |

| TMS/SWDIO | J4 | 9 | SWDIO |

| TCK/SWCLK | J4 | 7 | SWDCLK |

| RESET | J4 | 5 | RESET |

- Power the board via J1 9...22V.

- Verify the Connection with e.g. J-Link Commander. The output should look as follows:

Example Project

The following example project was created with the SEGGER Embedded Studio project wizard and runs out-of-the-box on the [SiliconVendor] [EvalBoardName].

It is a simple Hello World sample linked into the internal flash.

SETUP

- Embedded Studio: V7.20

- Hardware: Infineon EVAL PMG1 B1 DRP

- Link: File:Infineon CYPM1116 TestProject ES V720.zip