Difference between revisions of "NXP JN5189-DK006"

(→Minimum requirements) |

(→Example Project) |

||

| (10 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

__TOC__ |

__TOC__ |

||

| − | This article describes specifics for the NXP JN5189-DK006 |

+ | This article describes specifics for the NXP JN5189-DK006 evaluation board. The board supports different Upgrade boards. It can be used to test & verify QN9090 and JN5189 support. |

| − | [[File: |

+ | [[File:NXP_JN5189-DK006.jpg|450px]] |

== Minimum requirements == |

== Minimum requirements == |

||

| − | * |

+ | * J-Link software V6.74 or later |

| − | * J-Link software V6.54a or later |

||

== Preparing for J-Link == |

== Preparing for J-Link == |

||

| + | *Make sure that you install the correct "Upgrade Board" |

||

| − | The SiPeed Longan Nano does not come with a standard debug connector but populates the debug JTAG signals on 6 pads that can be found on the opposite of the USB-C interface. Therefore, it can be manually wired in case J-Link shall be connected to it. |

||

| + | *Connect the J-Link to the SWD header (P1) |

||

| − | |||

| + | *Power the board via external power supply / power jack (J4) |

||

| − | The following guide will describe how the Longan Nano Board can be connected to your J-Link Base V10 or higher. Other J-Links might work as well but wiring might be slightly different. All needed information can be found in the probe related documentation. |

||

| − | |||

| − | * The Longan Nano board does not come with the pin header populated so first the pin headers need to be soldered to your board. |

||

| − | * Now connect the board with e.g. jumperwires to your J-Link probe. |

||

| − | * The following table shows how the Signals should be connected on both the board and [https://www.segger.com/products/debug-probes/j-link/technology/interface-description/ J-Link] side. |

||

| − | |||

| − | {| class="wikitable" |

||

| − | |- |

||

| − | ! J-Link 20 pin debug interface !! Pin on eval board pads |

||

| − | |- |

||

| − | | Pin 1 (VTref) || 3V3 |

||

| − | |- |

||

| − | | Pin 4 (GND) || GND |

||

| − | |- |

||

| − | | Pin 5 (TDI) || JTDI |

||

| − | |- |

||

| − | | Pin 7 (TMS) || JTMS |

||

| − | |- |

||

| − | | Pin 9 (TCK) || JTCK |

||

| − | |- |

||

| − | | Pin 13 (TDO) || JTDO |

||

| − | |- |

||

| − | |} |

||

| − | The resulting connection will then look like this: |

||

| − | |||

| − | [[File:Longan_Nano.png|450px]] |

||

| − | * Power the board via the USB-C port. |

||

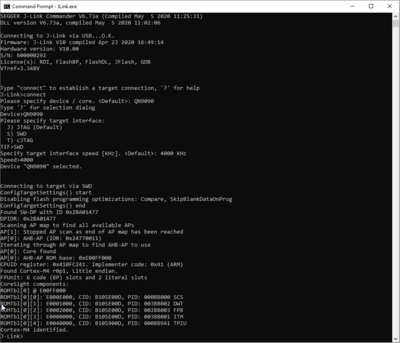

* Verify the Connection with e.g. [https://wiki.segger.com/J-Link_cannot_connect_to_the_CPU#Verify_functionality_using_J-Link_Commander J-Link Commander]. The output should look as follows: |

* Verify the Connection with e.g. [https://wiki.segger.com/J-Link_cannot_connect_to_the_CPU#Verify_functionality_using_J-Link_Commander J-Link Commander]. The output should look as follows: |

||

| − | [[File: |

+ | [[File:NXP_QN9090_Connect.PNG|400px]] |

| − | |||

| − | == Debugging in SEGGER Embedded Studio == |

||

| − | |||

| − | === Example projects for SEGGER Embedded Studio=== |

||

| − | The following example project was created with the SEGGER Embedded Studio project wizard and runs out-of-the-box on the Longan Nano board. It is a simple Hello World sample and can be downloaded here: |

||

| − | |||

| − | [[Media: GD32VF1xx_Hello_World.zip | Hello World sample ]] |

||

| − | __TOC__ |

||

| − | |||

| − | This article describes specifics for the SiPeed Longan Nano board based on a GigaDevice GD32VF103CB. |

||

| − | |||

| − | [[File:SiPeed_Lingan_Nano.jpg|250px]] |

||

| − | |||

| − | == Minimum requirements == |

||

| − | * RISC-V is supported by current J-Link models. In case of doubt, please check [[Software and Hardware Features Overview | Overview about which models / revisions support RISC-V]] |

||

| − | * Embedded Studio Version 4.30 or later |

||

| − | * J-Link software V6.54a or later |

||

| − | |||

| − | == Preparing for J-Link == |

||

| − | The SiPeed Longan Nano does not come with a standard debug connector but populates the debug JTAG signals on 6 pads that can be found on the opposite of the USB-C interface. Therefore, it can be manually wired in case J-Link shall be connected to it. |

||

| − | |||

| − | The following guide will describe how the Longan Nano Board can be connected to your J-Link Base V10 or higher. Other J-Links might work as well but wiring might be slightly different. All needed information can be found in the probe related documentation. |

||

| − | |||

| − | * The Longan Nano board does not come with the pin header populated so first the pin headers need to be soldered to your board. |

||

| − | * Now connect the board with e.g. jumperwires to your J-Link probe. |

||

| − | * The following table shows how the Signals should be connected on both the board and [https://www.segger.com/products/debug-probes/j-link/technology/interface-description/ J-Link] side. |

||

| − | |||

| − | {| class="wikitable" |

||

| − | |- |

||

| − | ! J-Link 20 pin debug interface !! Pin on eval board pads |

||

| − | |- |

||

| − | | Pin 1 (VTref) || 3V3 |

||

| − | |- |

||

| − | | Pin 4 (GND) || GND |

||

| − | |- |

||

| − | | Pin 5 (TDI) || JTDI |

||

| − | |- |

||

| − | | Pin 7 (TMS) || JTMS |

||

| − | |- |

||

| − | | Pin 9 (TCK) || JTCK |

||

| − | |- |

||

| − | | Pin 13 (TDO) || JTDO |

||

| − | |- |

||

| − | |} |

||

| − | The resulting connection will then look like this: |

||

| − | |||

| − | [[File:Longan_Nano.png|450px]] |

||

| − | * Power the board via the USB-C port. |

||

| − | * Verify the Connection with e.g. [https://wiki.segger.com/J-Link_cannot_connect_to_the_CPU#Verify_functionality_using_J-Link_Commander J-Link Commander]. The output should look as follows: |

||

| − | |||

| − | [[File:GD32VF1xx_Connect.PNG|400px]] |

||

| − | |||

| − | == Debugging in SEGGER Embedded Studio == |

||

| − | |||

| − | === Example projects for SEGGER Embedded Studio=== |

||

| − | The following example project was created with the SEGGER Embedded Studio project wizard and runs out-of-the-box on the Longan Nano board. It is a simple Hello World sample and can be downloaded here: |

||

| + | == Example Project== |

||

| − | [[Media: GD32VF1xx_Hello_World.zip | Hello World sample ]] |

||

| + | The following example project was created with the SEGGER Embedded Studio project wizard and runs out-of-the-box on the NXP JN5189-DK006. It is a simple Hello World sample linked into the internal flash.<br> |

||

| + | ====SETUP==== |

||

| + | *J-Link software: V6.74 |

||

| + | *Embedded Studio: V4.52b |

||

| + | *Hardware: NXP JN5189-DK006 (QN9090 upgrade board) |

||

| + | *Link: [[File:NXP_QN9090_TestProject_ES_V452b.zip]] |

||

Latest revision as of 11:32, 31 May 2021

This article describes specifics for the NXP JN5189-DK006 evaluation board. The board supports different Upgrade boards. It can be used to test & verify QN9090 and JN5189 support.

Minimum requirements

- J-Link software V6.74 or later

Preparing for J-Link

- Make sure that you install the correct "Upgrade Board"

- Connect the J-Link to the SWD header (P1)

- Power the board via external power supply / power jack (J4)

- Verify the Connection with e.g. J-Link Commander. The output should look as follows:

Example Project

The following example project was created with the SEGGER Embedded Studio project wizard and runs out-of-the-box on the NXP JN5189-DK006. It is a simple Hello World sample linked into the internal flash.

SETUP

- J-Link software: V6.74

- Embedded Studio: V4.52b

- Hardware: NXP JN5189-DK006 (QN9090 upgrade board)

- Link: File:NXP QN9090 TestProject ES V452b.zip