ONSemi RSL10 SiP

This article describes specifics for the ON Semiconductor RSL10 SiP evaluation board.

Minimum requirements

- J-Link software V6.89c or later

Preparing for J-Link

This step is very easy as the RSL10 SiP features a J-Link OB (on-board debugger) which works out-of-the-box.

- Connect the board via USB to the PC (USB is also used as power supply)

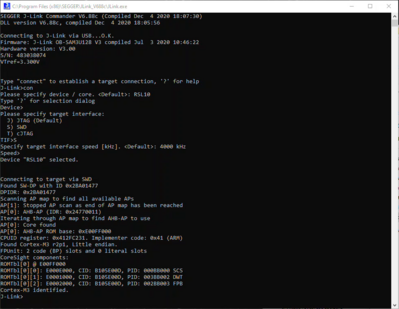

- Verify the Connection with e.g. J-Link Commander. The output should look as follows:

Example Application

The following example project was created with the SEGGER Embedded Studio project wizard and runs out-of-the-box on the ON Semiconductor RSL10 SiP EVB V1.2. It is a simple Hello World sample linked into the internal flash.

SETUP:

- J-Link software: V6.89c

- Embedded Studio: V5.10b

- Hardware: ON Semiconductor RSL10 SiP EVB V1.2

- Link: File:ONSemi RSL10 TestProject ES V510b.zip