Qorvo PAC5532EVK1

Revision as of 10:40, 30 September 2022 by SebastianB (talk | contribs) (Created page with "__TOC__ This article describes specifics for the Qorvo PAC5532EVK1 development platform. It can be used to test & verify PAC55xx device support. == Minimum requirements == *...")

This article describes specifics for the Qorvo PAC5532EVK1 development platform. It can be used to test & verify PAC55xx device support.

Minimum requirements

- J-Link software V7.82 or later

Preparing for J-Link

- Connect the J-Link to the SWD/JTAG connector (J13)

- Power the board via the VIN (J9) and GND (J11) connectors

- A voltage of 25V is required. See user manual for more information.

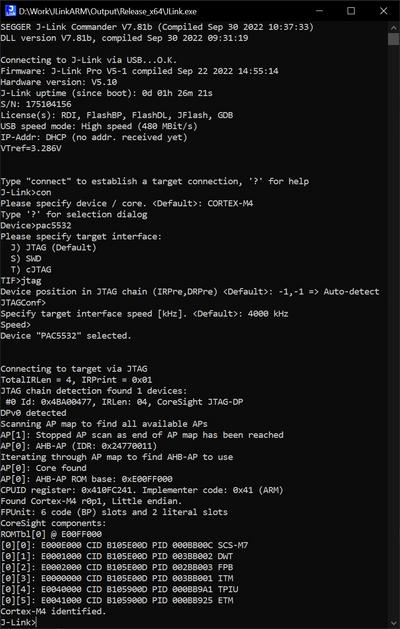

- Verify the Connection with e.g. J-Link Commander. The output should look as follows:

Example Project

The following example project was created with the SEGGER Embedded Studio project wizard and runs out-of-the-box on the Qorvo PAC5532EVK1 . It is a simple Hello World sample linked into the internal flash.

SETUP

- J-Link software: V7.82

- Embedded Studio: V6.32b

- Hardware: Qorvo PAC5532EVK1

- Link: File:Qorvo PAC5532EVK1 TestProject ES V632b.zip