Difference between revisions of "RTT Ramcode Sample for Cortex-M0+ (Keil MDK)"

| (11 intermediate revisions by one other user not shown) | |||

| Line 4: | Line 4: | ||

= Minimum requirements = |

= Minimum requirements = |

||

| − | In order to use |

+ | In order to use RTT on the ATMEL ATSAMD21 devices, the following minimum requirements have to be met: |

* J-Link software version V6.44g or later |

* J-Link software version V6.44g or later |

||

* µVision V5.24.2.0 or later (if the sample project from below shall be used) |

* µVision V5.24.2.0 or later (if the sample project from below shall be used) |

||

| Line 13: | Line 13: | ||

The following sample project is designed to be used with J-Link and Keil MDK to demonstrate RTT. The project has been tested with the minimum requirements mentioned above and a SAMD21 XPlained Pro evalboard. The sample project comes with a pre-configured project for Keil MDK that runs out-of-the box. |

The following sample project is designed to be used with J-Link and Keil MDK to demonstrate RTT. The project has been tested with the minimum requirements mentioned above and a SAMD21 XPlained Pro evalboard. The sample project comes with a pre-configured project for Keil MDK that runs out-of-the box. |

||

| − | [[Media: |

+ | [[Media:CortexM0+_RAM_RTT_Sample.zip | CortexM0+_RAM_RTT_Sample.zip ]] |

| + | |||

| + | = Manual = |

||

| + | *After downloading and unzipping the project, open it with Keil µVision V5.24.2.0 or later. |

||

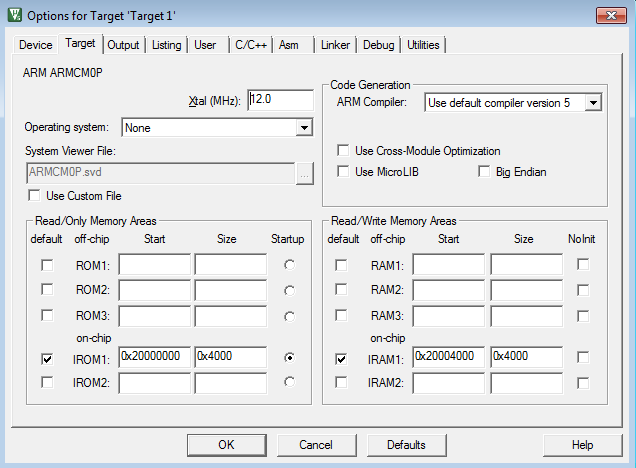

| + | *Remark: When using another Cortex M0+ device with different RAM sections, adapt the RAM sections accordingly in the Keil project settings: |

||

| + | <br>[[File:CortexM0+ RTT RAMSettings.PNG]] |

||

| + | *Build(F7) the project and start debugging by clicking on the Debug button (Ctrl + F5) |

||

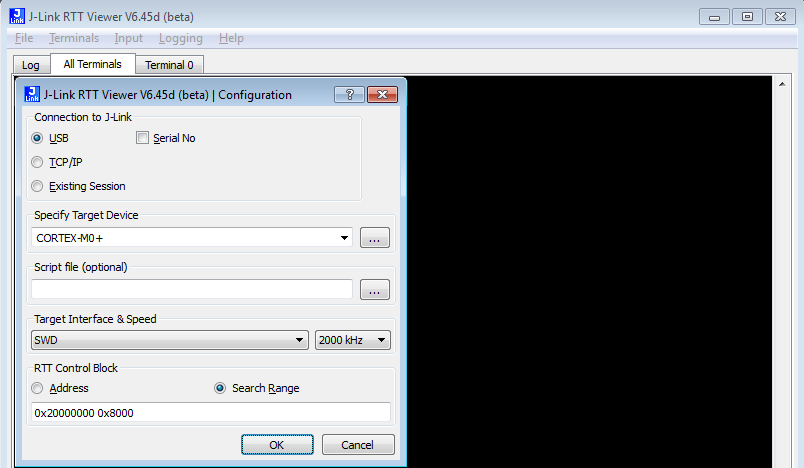

| + | *Start RTT Viewer and connect with the following settings: |

||

| + | [[File:CortexM0+_RTT_Settings.PNG|RTT Viewer Settings]] |

||

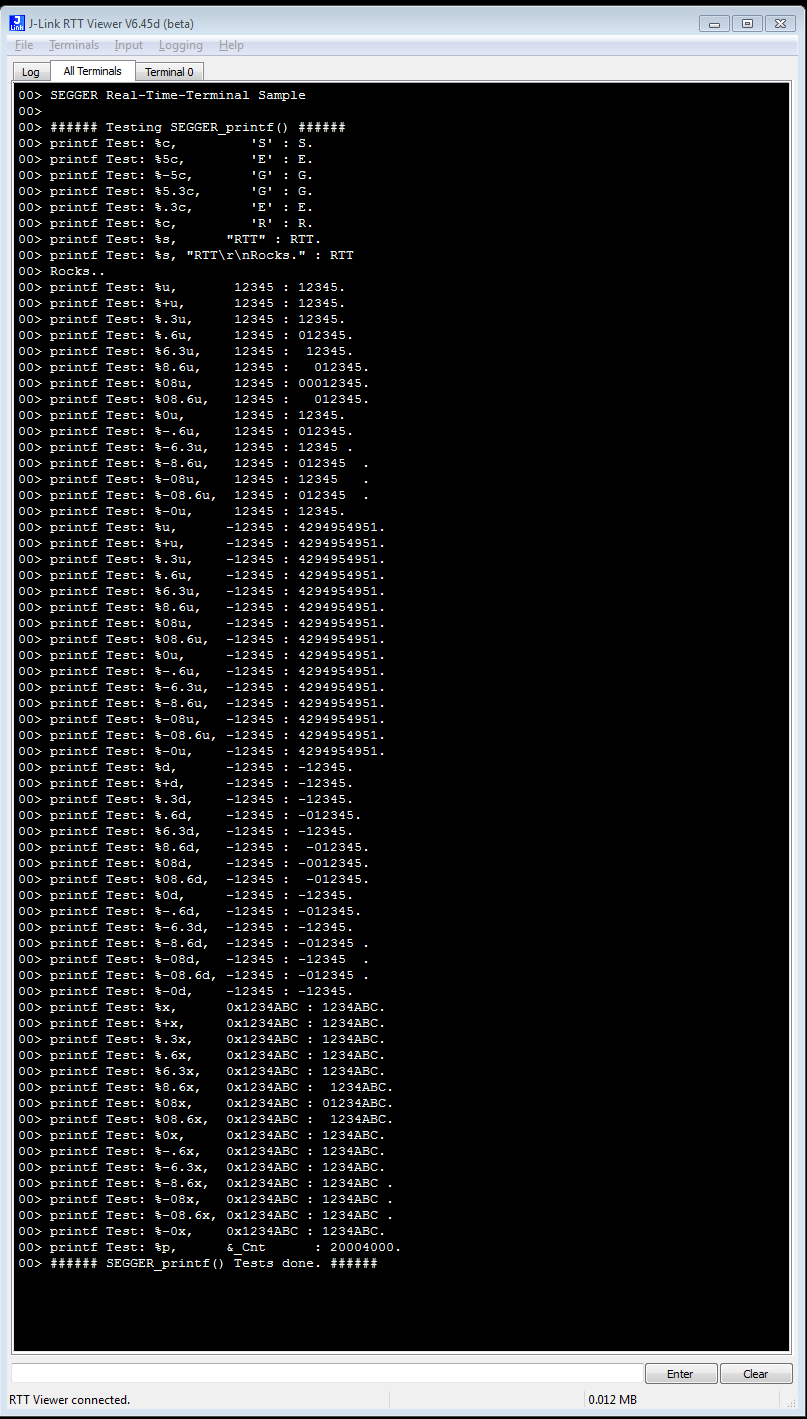

| + | *Running the ramcode (F5) in Keil results in the following output in RTT viewer:<br><br> |

||

| + | [[File:CortexM0+ RTT Output.PNG|RTT Viewer output]] |

||

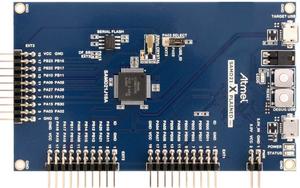

= Tested Hardware = |

= Tested Hardware = |

||

| − | [[File: |

+ | [[File:Atmel_SAMD21Xplained.jpg|left|thumb|SAMD21 XPlained Pro]] |

Latest revision as of 10:48, 28 January 2021

This article describes how to get started with RTT within RAM on a Cortex-M0+ device. This article assumes that there is already a basic knowledge about RTT in general (what is RTT, etc.). If this is not the case, we recommend to read RTT chapter in the J-Link User Manual (UM08001).

Minimum requirements

In order to use RTT on the ATMEL ATSAMD21 devices, the following minimum requirements have to be met:

- J-Link software version V6.44g or later

- µVision V5.24.2.0 or later (if the sample project from below shall be used)

- J-Link Plus HW version V10.1 or later

Sample project

RTT Ramcode

The following sample project is designed to be used with J-Link and Keil MDK to demonstrate RTT. The project has been tested with the minimum requirements mentioned above and a SAMD21 XPlained Pro evalboard. The sample project comes with a pre-configured project for Keil MDK that runs out-of-the box.

Manual

- After downloading and unzipping the project, open it with Keil µVision V5.24.2.0 or later.

- Remark: When using another Cortex M0+ device with different RAM sections, adapt the RAM sections accordingly in the Keil project settings:

- Build(F7) the project and start debugging by clicking on the Debug button (Ctrl + F5)

- Start RTT Viewer and connect with the following settings:

- Running the ramcode (F5) in Keil results in the following output in RTT viewer: