Difference between revisions of "Renesas RZ/A3UL SMARC EVK"

(→Preparing for J-Link) |

|||

| Line 12: | Line 12: | ||

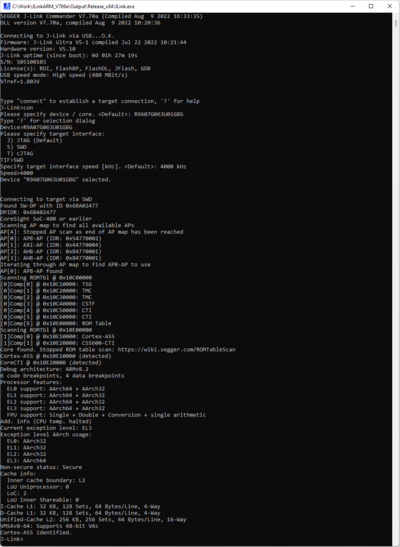

*Verify the Connection with e.g. [https://wiki.segger.com/J-Link_cannot_connect_to_the_CPU#Verify_functionality_using_J-Link_Commander J-Link Commander]. The output should look as follows: |

*Verify the Connection with e.g. [https://wiki.segger.com/J-Link_cannot_connect_to_the_CPU#Verify_functionality_using_J-Link_Commander J-Link Commander]. The output should look as follows: |

||

[[File:Renesas_RZ_A3UL_SMARC_Connect.PNG|400px]] |

[[File:Renesas_RZ_A3UL_SMARC_Connect.PNG|400px]] |

||

| + | |||

== Example Project== |

== Example Project== |

||

*N/A |

*N/A |

||

Revision as of 10:52, 11 August 2022

This article describes specifics for the Renesas RZ/A3UL SMARC evaluation board. The board supports different boot / power modes.

Minimum requirements

- J-Link software V7.70a or later

Preparing for J-Link

- Connect the J-Link to the SWD header (CN2)

- Power the board via USB-C (5V / 3A)

- Press the POWER button for a few seconds until the Carrier PWR On led turns on

- Verify the Connection with e.g. J-Link Commander. The output should look as follows:

Example Project

- N/A