Difference between revisions of "SiFive Arty FPGA Dev Kit"

(→Preparing for J-Link) |

(→Preparing for J-Link) |

||

| Line 7: | Line 7: | ||

In the following, it is described how the pins of connector JD on the ARTY board needs to be wired to J-Link. All pins of the J-Link side refer to the standard 0.1" 20-pin connector of J-Link. |

In the following, it is described how the pins of connector JD on the ARTY board needs to be wired to J-Link. All pins of the J-Link side refer to the standard 0.1" 20-pin connector of J-Link. |

||

| + | |||

| + | {| class="wikitable" |

||

| + | |+Wiring connection |

||

| + | ! Pin ARTY |

||

| + | ! Pin J-Link |

||

| + | ! Description |

||

| + | |- |

||

| + | |STM32F0 |

||

| + | |Cortex-M0 |

||

| + | |scope="col" style="text-align:center" | [[File:YES.png|20px|link=]] |

||

| + | |- |

||

| + | |} |

||

| + | |||

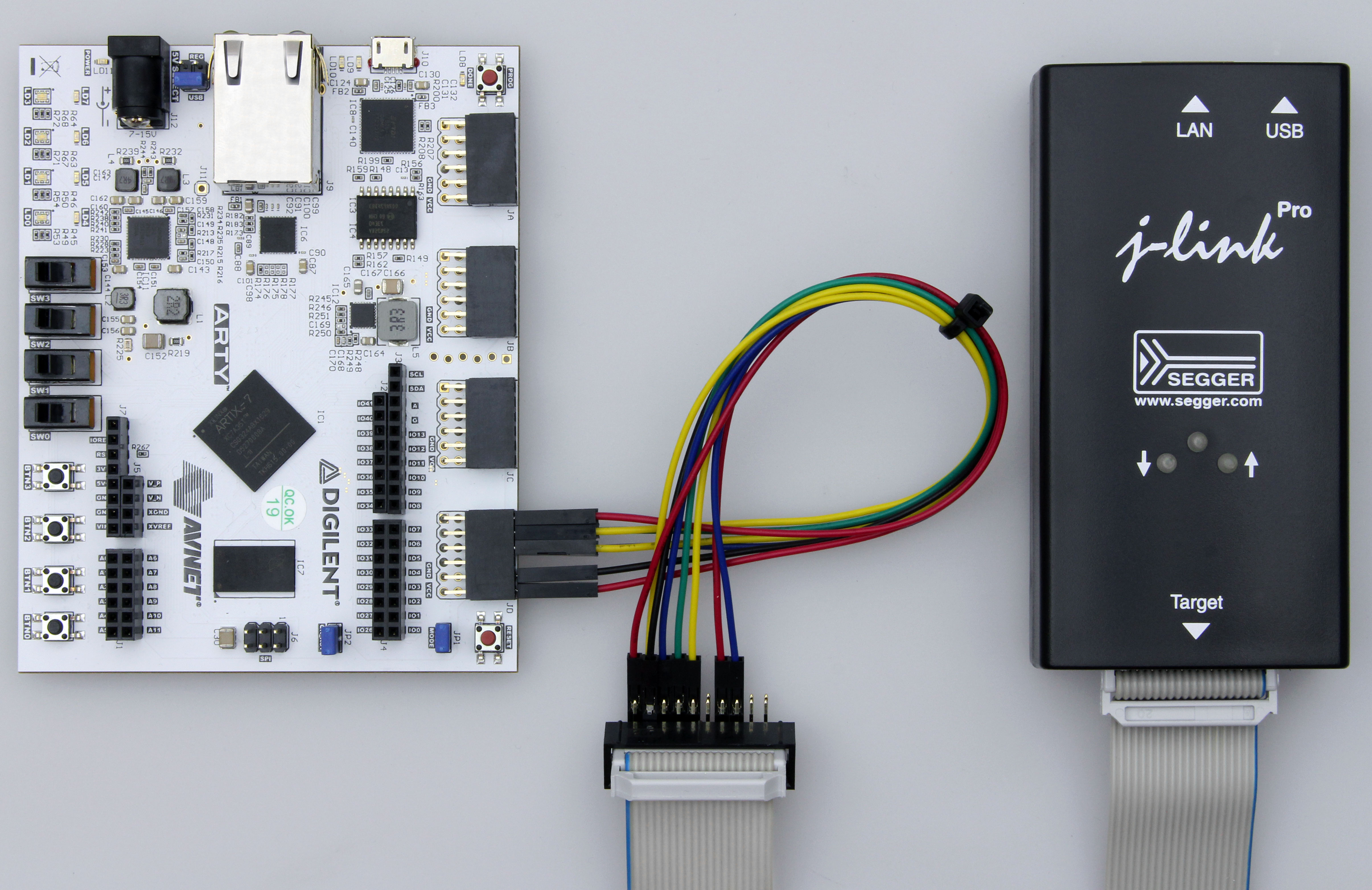

[[File:Wiki-sifive_arty_board.png]] |

[[File:Wiki-sifive_arty_board.png]] |

||

Revision as of 19:00, 1 September 2017

Contents

This article describes specifics for the SiFive Arty FPGA Dev Kit.

Preparing for J-Link

The SiFive Arty FPGA Dev Kit does not come with a standard debug connector but populates the debug JTAG signals on a custom connector. Therefore, it needs to be manually wired in case J-Link shall be connected to it.

In the following, it is described how the pins of connector JD on the ARTY board needs to be wired to J-Link. All pins of the J-Link side refer to the standard 0.1" 20-pin connector of J-Link.

| Pin ARTY | Pin J-Link | Description |

|---|---|---|

| STM32F0 | Cortex-M0 |