Difference between revisions of "NXP S32K3xx"

(→Multi-Core Debug Support) |

|||

| Line 25: | Line 25: | ||

==HSE activated== |

==HSE activated== |

||

When the HSE (Hardware Secure Engine) is activated (HSE Firmware Usage Feature flag in the UTEST at location 0x1B000000 is set) the access to the last 36 sectors in the last code flash memory (either block 1 @ 0x00500000 or block 3 @ 0x00700000 ) is prohibited. |

When the HSE (Hardware Secure Engine) is activated (HSE Firmware Usage Feature flag in the UTEST at location 0x1B000000 is set) the access to the last 36 sectors in the last code flash memory (either block 1 @ 0x00500000 or block 3 @ 0x00700000 ) is prohibited. |

||

| − | ==Multi-Core |

+ | ==Multi-Core Support== |

| + | Before proceeding with this article, please check out the generic article regarding Multi-Core debugging [[Multi-Core_Debugging | here]]. |

||

When it comes to multi-core debugging it's very specific to the device and use case, how the debugger should behave |

When it comes to multi-core debugging it's very specific to the device and use case, how the debugger should behave |

||

The S32K3 family comes with a wide range of feature sets. Some devices from this family feature a secondary core which is disabled after reset / by default. |

The S32K3 family comes with a wide range of feature sets. Some devices from this family feature a secondary core which is disabled after reset / by default. |

||

| + | |||

==Reset== |

==Reset== |

||

The J-Link performs a device specific reset sequence.<br>'''NOTE:''' The reset pin needs to be connected in order to guarantee a proper reset. |

The J-Link performs a device specific reset sequence.<br>'''NOTE:''' The reset pin needs to be connected in order to guarantee a proper reset. |

||

Revision as of 15:24, 30 January 2023

Contents

The S32K3 family from NXP includes Cortex-M7 based MCUs in single or dual core configurations supporting ASIL B/D safety applications. The S32K3 family is supported since J-Link software version V6.89c.

NOTE: There are different device configurations available. For details regarding which configurations are available and which are supported by the J-Link software, please get in touch with NXP (NDA required). Due to the fact that most device information are under NDA, SEGGER is allowed to provide very limited support, only. If you encounter any issues with the S32K3 device support, we recommend to get in touch with NXP directly. They will involve us if required.

Internal Flash

Supported Regions

Following flash regions are supported by the J-Link:

- Code flash memory 0 (0x00400000 - 0x004FFFFF)

- Code flash memory 1 (0x00500000 - 0x005FFFFF)

- Code flash memory 2 (0x00600000 - 0x006FFFFF)

- Code flash memory 3 (0x00700000 - 0x007F3FFF)

- Data flash memory (0x10000000 - 0x1003FFFF)

RAM

The ITCM and DTCM must be properly initialized with correct ECC before any read operation to avoid any code runaway or software malfucntion or core lockup. ITCM must be initialized with 64-bit writes whereas DTCM can be initialized with 32-bit or 64-bit writes. The following memory ranges are initialized by the J-Link on connect by default. Other ranges needs to be initialized by the application / boot ROM.

| Memory | Address | Size |

|---|---|---|

| DTCM0 | 0x20000000 | 32 KB |

| SRAM0 | 0x20400000 | 16 KB |

HSE activated

When the HSE (Hardware Secure Engine) is activated (HSE Firmware Usage Feature flag in the UTEST at location 0x1B000000 is set) the access to the last 36 sectors in the last code flash memory (either block 1 @ 0x00500000 or block 3 @ 0x00700000 ) is prohibited.

Multi-Core Support

Before proceeding with this article, please check out the generic article regarding Multi-Core debugging here. When it comes to multi-core debugging it's very specific to the device and use case, how the debugger should behave The S32K3 family comes with a wide range of feature sets. Some devices from this family feature a secondary core which is disabled after reset / by default.

Reset

The J-Link performs a device specific reset sequence.

NOTE: The reset pin needs to be connected in order to guarantee a proper reset.

Limitations

Attach

Attach is not supported by default because the J-Link initializes certain RAM regions by default.

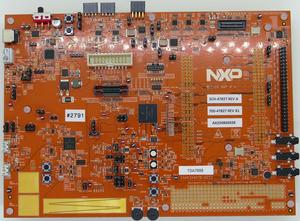

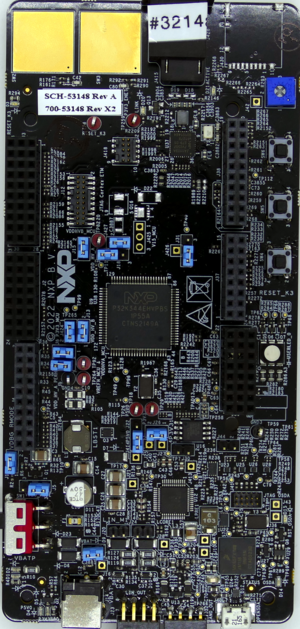

Evaluation Boards

- NXP S32K3X4EVB-Q257 evaluation board: https://wiki.segger.com/NXP_S32K3X4EVB

- NXP XS32K3XXCVB-Q257 evaluation board: https://wiki.segger.com/NXP_XS32K3XXCVB

- NXP X32K3XXEVB-Q172 evaluation board: https://wiki.segger.com/NXP_X32K3XXEVB

Example Application

- NXP S32K3X4EVB evaluation board: https://wiki.segger.com/NXP_S32K3X4EVB#Example_Project

NOTE: The example has been tested on the S32K3X4EVB but it should run on any S32K344 based hardware.

Tracing on NXP S32K344

Minimum requirements

In order to use trace on the NXP S32K344 MCU devices, the following minimum requirements have to be met:

- J-Link software version V7.70c or later

- Ozone V3.26h or later (if streaming trace and / or the sample project from below shall be used)

- J-Trace PRO (for Cortex-M) HW version V1.0 or later for streaming trace

To rebuild the project our IDE Embedded Studio can be used. The recommended version to rebuild the projects is V6.30. But the examples are all prebuild and work out-of-the box with Ozone, so rebuilding is not necessary.

Streaming trace

The project has been tested with the minimum requirements mentioned above and the following two eval board:

- S32K3X4EVB-Q257: NXP_S32K344_TracePins.zip

- S32K3X4EVB-T172: NXP_S32K344_S32K3X4EVB_TracePins.zip

Trace buffer (TMC/ETB)

The project below is utilizing the on-chip trace buffer (it is not meant for streaming trace) and works with any NXP S32K344 board.

- Example project: NXP_S32K344_TraceBuffer.zip

Tested Hardware

Specifics/Limitations

The S32K3X4EVB_T172 needs some solder bridges closed and resistors removed for all 4 trace data pins to work. For more information about this see the board specific schematics.

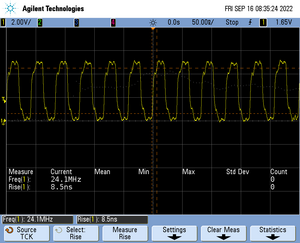

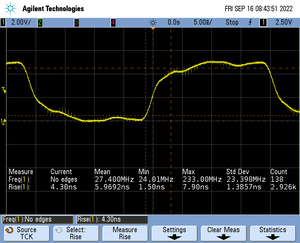

Reference trace signal quality

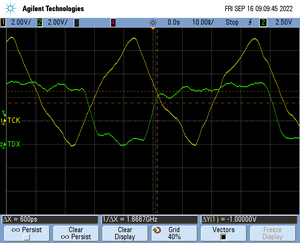

The following pictures show oscilloscope measurements of trace signals output by the NXP S32K3X4EVB-Q257 using the example project. All measurements have been performed using a Agilent InfiniiVision DSO7034B 350 MHz 2GSa/s oscilloscope and 1156A 1.5 GHz Active Probes. If your trace signals look similar on your trace hardware, chances are good that tracing will work out-of-the-box using the example project. More information about correct trace timing can be found at the following website.

Trace clock signal quality

The trace clock signal quality shows multiple trace clock cycles on the tested hardware as reference.

Rise time

The rise time of a signal shows the time needed for a signal to rise from logical 0 to logical 1. For this the values at 10% and 90% of the expected voltage level get used as markers. The following picture shows such a measurement for the trace clock signal.

Setup time

The setup time shows the relative setup time between a trace data signal and trace clock. The measurement markers are set at 50% of the expected voltage level respectively. The following picture shows such a measurement for the trace data signal 0 relative to the trace clock signal.